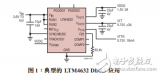

DN551 - 用于 DDR、QDR 和 QDR-IV SRAM 的超薄型三路输出 μModule 稳压器可安放在 0.5cm2 面积内和 PCB 的背面

2019-05-06 08:40

数据速率下的一项主要挑战是保持在 SRAM 与高速 FPGA 和处理器等器件之间传输数据的完整性。 一种良好的解决方案是把 SRAM (例如:QDR-IV、 QDR 或 DDR) 布设得非常靠近 PCB

2017-05-08 15:56

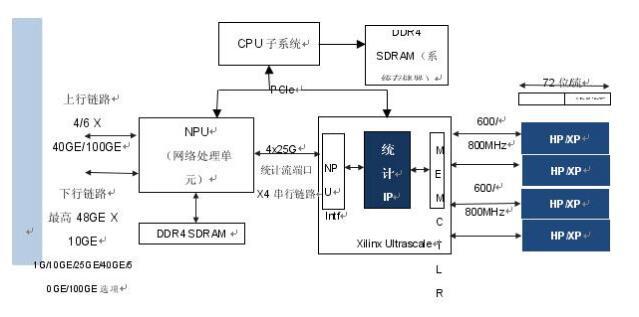

—修改—写操作。本文将描述一种使用IP方法的独特统计计数器,这种计数器的一端可以连接网络处理器(NPU),另一端可以连接Xilinx公司的QDR-IV存储控制器。QDR-IV统计计数器IP是一种带有QDR-IV SR

2019-07-17 06:55

。Cyclone IV 器件在电气方面提供了对QDR II 接口的支持,但是对于 QDR II 接口,Altera 没有提供控制器或者物理层 (PHY)宏功能。

2017-11-14 10:12

流媒体视频、云服务和移动数据推动了全球网络流量的持续增长。为了支持这种增长,网络系统必须提供更快的线路速率和每秒处理数百万个数据包的性能。在网络系统中,数据包的到达顺序是随机的,且每个数据包的处理需要好几个存储动作。数据包流量需要每秒钟访问数亿万次存储器,才能在转发表中找到路径或完成数据统计。 数据包速率与随机存储器访问速率成正比。

2018-01-29 11:30

网络路由器带有用于性能监控、流量管理、网络追踪和网络安全的统计计数器。计数器用来记录数据包到达和离开的次数以及特定事件的次数,比如当网络出现坏包时。数据包的到达会使多个不同的统计计数器发生更新;但一台网络设备中的统计计数器的数量及其更新速度常常受到存储技术的限制。

2018-09-23 14:00

流媒体视频、云服务和移动数据推动了全球网络流量的持续增长。为了支持这种增长,网络系统必须提供更快的线路速率和每秒处理数百万个数据包的性能。在网络系统中,数据包的到达顺序是随机的,且每个数据包的处理需要好几个存储动作。数据包流量需要每秒钟访问数亿万次存储器,才能在转发表中找到路径或完成数据统计。 数据包速率与随机存储器访问速率成正比。如今的网络设备需要具有很高的随机访问速率(RTR)性能和高带宽才能跟上如今

2017-12-06 10:55

些位置可以访问各组 (bank) 内可用的 BUFIO。对于 x36 宽的 QDR II SRAM 接口,CQ_P 和 CQ_N 均用来采集读数据(第 11 页图9)。一个Virtex-5 器件中的每个

2019-04-22 07:00

本章介绍了 Cyclone® IV 器件所支持的边界扫描测试 (BST) 功能。这些 BST 功能与Cyclone III 器件中的相类似,除非另有说明。Cyclone IV

2017-11-14 10:50

电子专业单片机相关知识学习教材资料之Cyclone_IV器件中的SEU缓解

2016-09-02 16:54