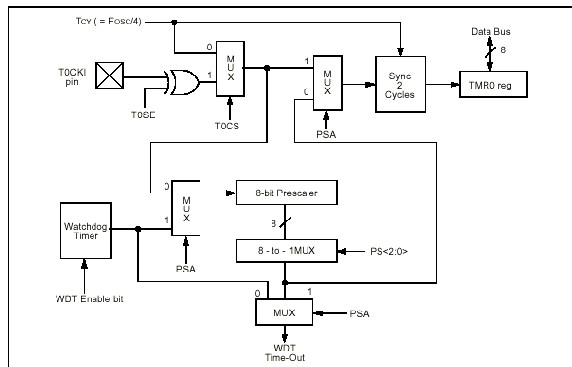

1、从RTCC到WDT的改变 MOVLW B‘XX0X0XXX’ ;选择内部时钟和新的预分频值 OPTION ;如果新的预分频值=“000”或者 CLRF

2018-11-08 16:14

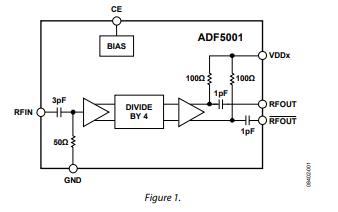

ADF5001预分频器是一款低噪声、低功耗、固定RF分频器模块 ,可用来将高达18GHz的频率分频至适合输入到[ADF4156]或 [ADF4106]等PLL IC的较低频率。ADF5001提供4

2025-04-16 15:50

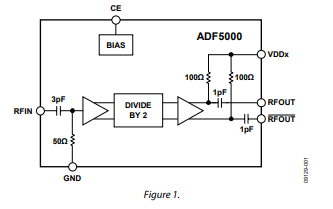

ADF5000预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18 GHz的频率分频至适合输入到[ADF4156]等PLL IC的较低频率。ADF5000提供2分

2025-04-16 15:16

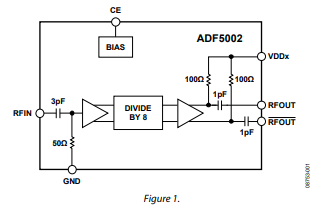

ADF5002预分频器是一款低噪声、低功耗、固定RF分频器模块,可用来将高达18GHz的频率分频至适合输入到 [ADF4156]或[ADF4106]等PLL IC的较低频率。ADF5002提供8

2025-04-16 15:46

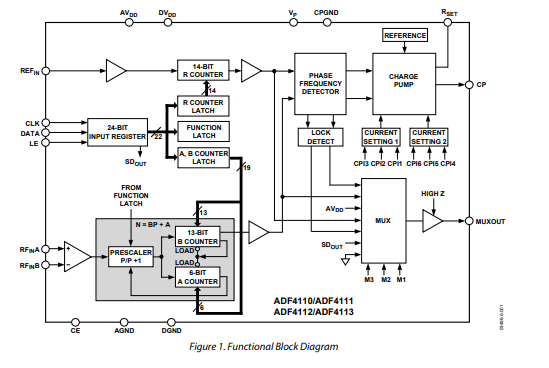

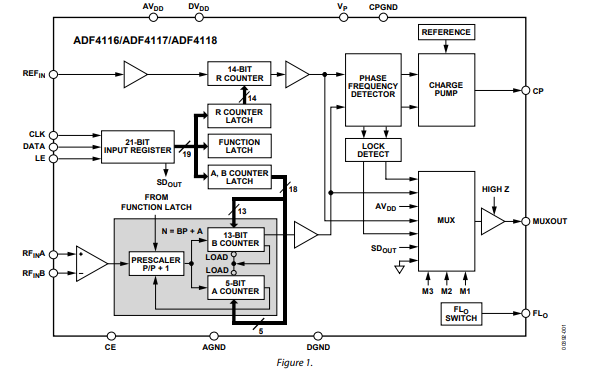

/P+1)组成。A(6位)、B(13位)计数器与双模预分频器(P/P+1)配合,可实现N分频器(N = BP+A)。此外,14位参考分频器(R分频器)允许PFD输入端的

2025-04-27 10:43

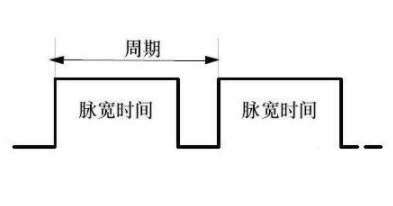

对于pwm,想必很多朋友都有所耳闻。但是,大家对于pwm真的了解吗?譬如,pwm频率是如何被确定下来的?pwm频率和pwm

2020-12-12 09:55

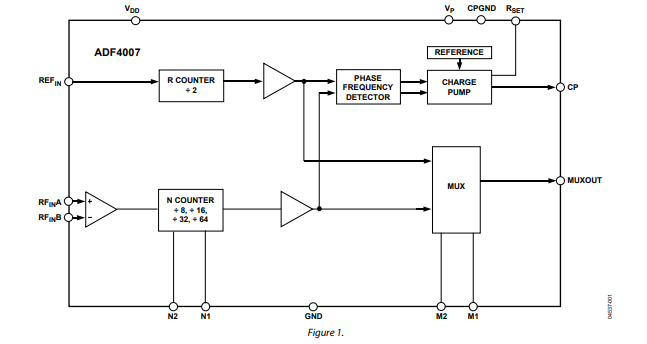

器/预分频器组成。分频器/预分频器值可以通过两个外部控制引脚设置为四个值中的一个(8、16、32或64)。参考

2025-04-27 15:23

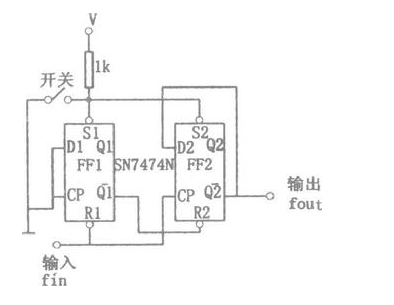

初学 Verilog 时许多模块都是通过计数与分频完成设计,例如 PWM 脉宽调制、频率计等。而分频逻辑往往通过计数逻辑完成。本节主要对偶数分频、奇数

2023-03-29 11:38

从分频方式看可以分为两种,一种是主动分频(PassiveCrossover),或者叫电子分频,也可以叫外置分频、有源分频

2019-10-08 10:37

A和B计数器以及双模预分频器(P/P+1)组成。A(5位)、B(13位)计数器与双模预分频器(P/P+1)配合,可实现N分频器(N = BP+A)。此外,14位参考分频

2025-04-27 15:01