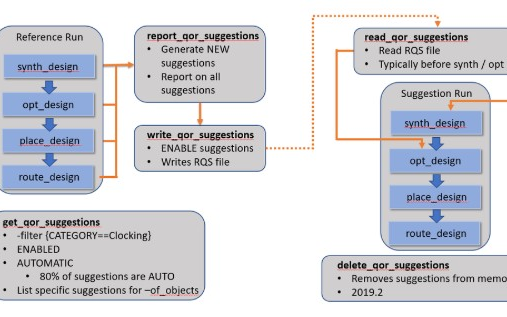

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具行为的设计单元属性的解决方案,即便在无法自动执行解决方案的情况下也可提供文本修改建议。

2020-01-24 17:27

report_failpast除了基本的使用方法(不添加任何选项)之外,还提供了其他的选项。例如,-pblock选项可用于分析Pblock对应的约束是否合理。该选项可在布局之前使用(要求已经提供了Pblock具体位置约束),也可在布局之后使用。

2018-11-13 10:35

这次我们要介绍的GUI上的按键是Summary Report。这个按键其实很简单,就是调用summaryReport这个命令,点一下会出现如下界面

2020-05-19 16:49

Report QoR Suggestions (RQS) 可识别设计问题,并提供工具开关和可影响工具行为的设计单元属性的解决方案,即便在无法自动执行解决方案的情况下也可提供文本修改建议。

2023-07-19 10:38

即设计规则检查,通过Checklist和Report等检查手段,重点规避开路、短路类的重大设计缺陷,检查的同时遵循PCB设计质量控制流程与方法。

2020-06-24 10:14

PCB拼板是PCB厂经常要做的事情,进行拼板需要注意哪些事项?PCB拼板有哪些要则?

2019-05-31 09:36

本文详细介绍什么是pcb打样,对pcb打样是什么意思作全面的讲解,对您全面了解pcb打样加工有帮助。

2014-04-22 22:32

如果选择Synth and Impl,会生成两个文件:RQSPreSynth.tcl和RQSImplCommon.tcl。Project模式下,RQSPreSynth.tcl可作为约束文件直接添加到Constraint Set里(Vivado支持.tcl文件作为约束文件,添加时将文件类型切换为.tcl即可,如图6所示)。

2019-01-15 16:48

《XDC 约束技巧》系列中讨论了XDC 约束的设置方法、约束思路和一些容易混淆的地方。我们提到过约束是为了设计服务,写入 Vivado中 的 XDC 实际上就是用户设定的目标,Vivado对 FPGA 设计的实现过程必须以满足 XDC 中的约束为目标进行。那我们如何验证实现后的设计有没有满足时序要求?又如何在开始布局布线前判断某些约束有没有成功设置?或是验证约束的优先级?这些都要用到 Vivado 中的静态时序分析工具。

2023-05-04 11:20

AD封装转ALLEGRO封装时,要把所有封装放到一张PCB上或者分批次的放到PCB上,把PCB转成ALLEGRO格式的,然后再用ALLEGRO导出PCB封装

2018-04-05 17:06