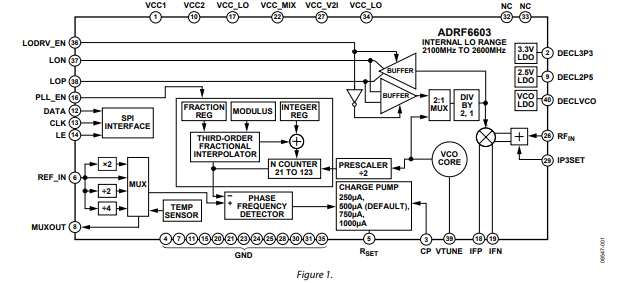

ADRF6603是一款高动态范围有源混频器,集成小数N分频锁相环(PLL)和压控振荡器(VCO),用于内部混频器LO的产生。 ADRF6603与ADRF6602共同构成了一个集成PLL/混频器系列,涵盖2100

2025-03-28 16:48

介绍在双模式(模拟放大器和数字 TDMA)蜂窝电话中设置 PLL 分频器值的方法。概述了IS-136双模电话频率计划,使用119.64MHz的第一中频和455kHz的放大器中频。需要在

2023-02-23 18:20

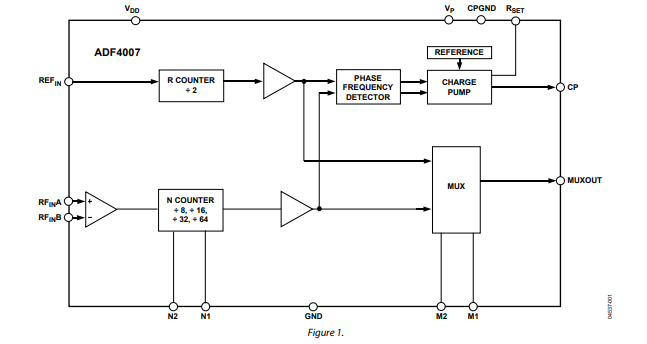

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和

2025-04-27 15:23

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和

2023-02-24 17:39

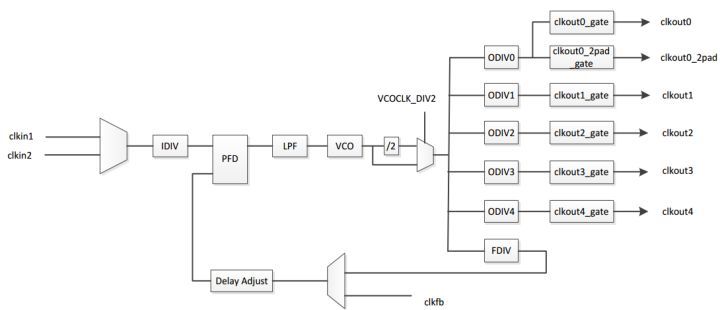

很多初学者看到板上只有一个50Mhz时钟输入的时候都产生疑惑,时钟怎么才50Mhz?如果要工作在100Mhz、150Mhz怎么办?在很多FPGA芯片内部都集成了

2021-02-04 13:22

输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25MHz、50MHz和100

2018-04-24 11:20

STM32中有一个全速功能的USB模块,其串行接口引擎需要一个频率为48MHz的时钟源。该时钟源只能从PLL输出端获取,可以选择为1.5分频或者1分频,也就是,当需要使

2017-11-30 09:14

为什么单片机内置时钟源不经过pll也可以分频? 单片机内置时钟源不经过PLL也可以实现分频,原因在于单片机内置时钟源自带分频

2023-09-02 15:12

分频器设计 一:分频器概念 板载时钟往往 是 有限个( 50MHZ/100MHZ/24MHZ/60

2023-11-03 15:55

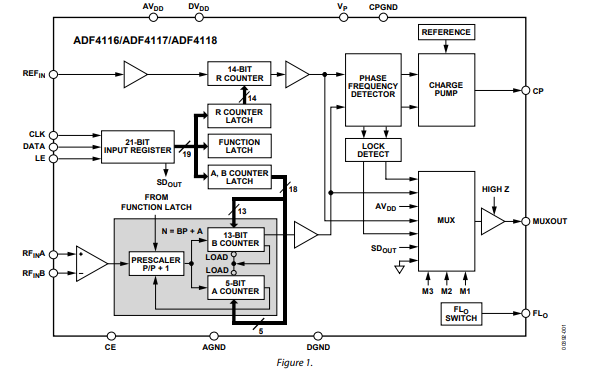

ADF4116/ADF4117/ADF4118均为频率合成器,可以用来在无线接收机和发射机的上变频和下变频部分实现本振。上述器件由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器、可编程

2025-04-27 15:01