电子发烧友网为你提供()集成整数 N 分频 PLL 和 VCO 的 350-5000 MHz 宽带接收混频器相关产品参数、数据手册,更有集成整数 N 分频

2025-05-22 18:31

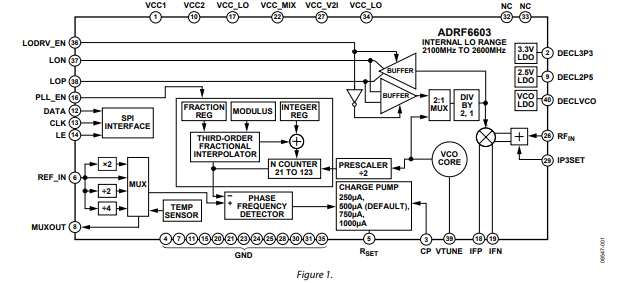

ADRF6603是一款高动态范围有源混频器,集成小数N分频锁相环(PLL)和压控振荡器(VCO),用于内部混频器LO的产生。 ADRF6603与ADRF6602共同构成了一个集成PLL/混频器系列,涵盖2100

2025-03-28 16:48

电子发烧友网为你提供()无杂散、50 MHz 至 2.1 GHz 单通道小数 N 分频频率合成器相关产品参数、数据手册,更有无杂散、50

2025-05-23 18:30

ADRF6806:50 MHz至525 MHz正交解调器,带小数N PLL和压控振荡器数据表

2021-05-24 18:27

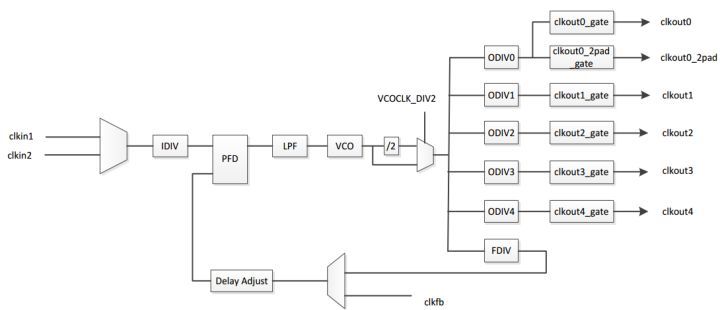

8.17所示,本实例将用到FPGA内部的PLL资源,输入FPGA引脚上的25MHz时钟,配置PLL使其输出4路分别为12.5MHz、25

2018-04-19 19:00

介绍在双模式(模拟放大器和数字 TDMA)蜂窝电话中设置 PLL 分频器值的方法。概述了IS-136双模电话频率计划,使用119.64MHz的第一中频和455kHz的放大器中频。需要在

2023-02-23 18:20

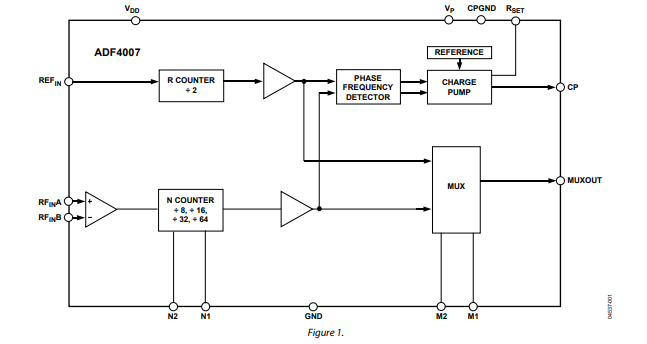

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和

2025-04-27 15:23

ADF4007是一款高频分频器/PLL频率合成器,可用于各种通信应用。RF端工作频率可达7.5 GHz,PFD端工作频率可达120 MHz。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵和

2023-02-24 17:39

很多初学者看到板上只有一个50Mhz时钟输入的时候都产生疑惑,时钟怎么才50Mhz?如果要工作在100Mhz、150Mhz怎么办?在很多FPGA芯片内部都集成了

2021-02-04 13:22

UG-160: 整数N分频PLL频率合成器评估板

2021-03-20 10:17