pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,

2023-09-02 14:59

时钟,由外接晶振产生,稳定性高HSEOSC2~26MHz高速外部时钟。由外接晶振产生(外部晶振一般都是8MHz)HSIRC16MHz告诉内部时钟,由内部RC振荡器产生PLL锁相环倍频

2021-08-02 08:57

PLL锁相环倍频是一种用于改变输入信号频率的技术,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56

或外部时钟,频率范围为4~16MHz。LSI:低速内部时钟源,RC振荡器,频率为40KHz。LSE:低速外部时钟源,接频率为32.768KHz的石英晶体。PLL:锁相环倍频输出

2021-08-23 08:24

锁相环是如何实现倍频的? 锁相环(Phase Locked Loop, PLL)是一种电路,用于稳定和恢复输入信号的相位和频率。它可以广泛应用于通信、计算机、音频等领

2023-09-02 14:59

锁相环(PLL),锁相环(PLL)是什么意思 PLL的概念 我们所说的

2010-03-23 10:47

pll锁相环的作用 pll锁相环的三种配置模式 PLL锁相环是现代电子

2023-10-13 17:39

Actel FPGA PLL锁相环的最大能达到几倍频几分频?我在网上查了一下有人说是20倍频,10分频,但是我没有在芯片手册里面找到资料,想要确认一下。

2014-12-04 11:25

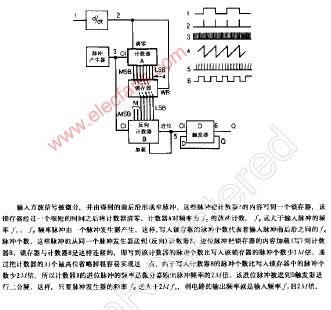

不带锁相环的倍频器

2009-09-17 16:11

在电子和通信领域,倍频器和锁相环(PLL)是两种常见的电路结构,它们在信号处理、频率合成和通信系统中扮演着重要角色。尽管两者在某些方面存在相似之处,但它们在功能、工作原理和应用领域等方面存在显著差异。本文将对

2024-06-20 11:34