本应用笔记介绍了ADI公司的DS314xx时钟同步IC如何进行现场升级,以接受并锁定至1Hz输入时钟信号。它还描述了在少数情况下需要1Hz时钟监控功能和系统软件支持。有了这些元件,使用DS314xx器件构建的系统就

2023-03-08 15:22

电信系统必须与1Hz或1PPS(每秒一个脉冲)输入时钟信号同步。例如,这种定时信号可能来自GPS接收器或IEEE® 1588从功能。

2023-01-29 19:05

AD9554 是一款低环路带宽时钟转换器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554产生的输出时钟

2025-04-10 11:51

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buff

2017-02-09 12:54

AD9547针对许多系统提供同步功能,包括同步光纤网络(SONET/SDH)。该器件产生的输出时钟可以与两路差分或四路单端外部输入参考

2025-04-11 09:37

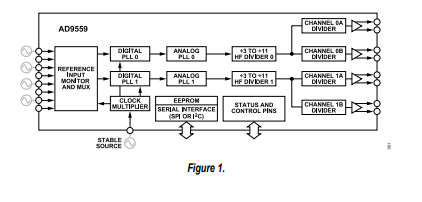

AD9559是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。AD9559产生的输出时钟

2025-04-10 14:35

,以确保视频信号的同步和稳定。以下是关于视频时钟合成芯片的使用指南: 1. 视频时钟合成芯片的基本概念 视频时钟合成芯片是一种数字电路,它通过相位锁定环(Phase-L

2024-10-10 11:17

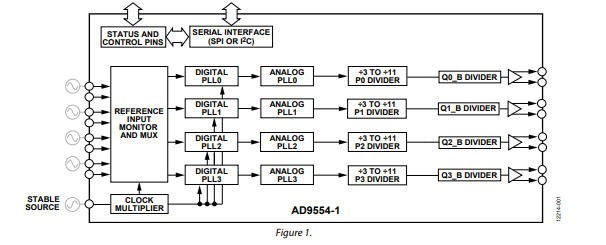

AD9554-1是一款低环路带宽时钟倍频器,可针对包括同步光纤网络(SONET/SDH)的许多系统提供抖动清除和同步功能。 AD9554-1产生的输出时钟

2025-04-10 11:21

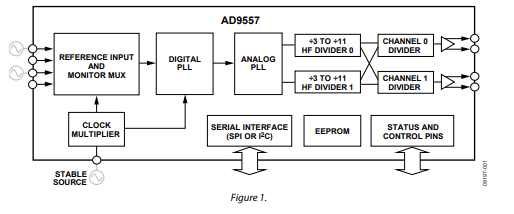

(PLL)可以降低与外部参考时钟相关的输入时间抖动或相位噪声。即使所有参考输入都失效,AD9557的数字控制环路和保持电

2025-04-10 14:42

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也

2020-03-29 17:19