频率源可以说是一个通信系统的心脏,心脏的好坏很大程度上决定着一个机体的健康状况,而锁相环又是频率源的主要组成部分,因此性能优异的锁相环芯片对于通信系统来说是非常重要的。锁相环的相位噪声对电子设备

2017-11-25 13:38

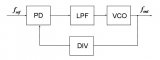

信号频率对输入信号频率的自动跟踪,一般用于闭环跟踪电路。是无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC (锁相环集成电路),压控振荡器给出一个信号,一部分作为输出

2017-12-13 16:26

合成技术实现的频率源已在通信、电视等领域得了广泛应用。本文介绍的ADl公司的ADF4360系列芯片就是用于无线通信射频系统(GSM,DECT,PCS,WCDMA。DCS)基站和WLAN混频电路的一款性价比很高,且应用范围较广的锁相芯片。

2020-08-17 15:47

数电这块,它跟PLL芯片有关,就是925芯片。CPU本身是有PWM输出能力的,但还是选用了PLL芯片来做正弦波的前置,这

2018-06-08 10:26

一个板子下来,3-6种时钟需求常见,不同的频率,不同的电平标准。硬件工程师做设计,不同板卡,各种设计混合在一块,库房有10多种晶振,时钟驱动芯片,时钟PLL芯片,琳琅满目。针对FPGA的设计,Microchip有一块

2022-09-20 11:03

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和对之间在PCB上传输延时要求较低,主要依靠锁相环(PLL)和芯片的时钟数据恢复功能。

2019-09-20 14:12

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

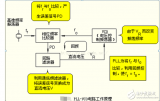

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

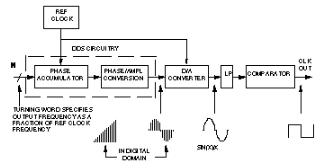

新的集成完整DDS产品为敏捷频率合成应用提供了一种有吸引力的模拟PLL替代方案。长期以来,直接数字频率合成 (DDS) 一直被认为是生成高精度、频率捷变(宽范围内可快速变化的频率)、低失真输出波形的卓越技术。

2023-01-30 09:51