SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52

锁相环 (PLL) 是电子系统中最通用、最灵活和最有价值的电路配置之一,因此在许多应用中都有使用。它用于时钟重定时和恢复,作为频率合成器和可调谐振荡器,仅举几个例子。因此,在包括无线电接收器和测试

2023-07-10 09:57

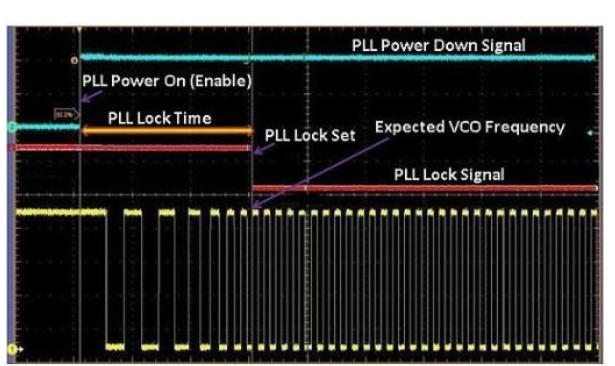

PLL锁定有那些检测方法,它们特点是什么?一种是最为简单的数字检测,它利用输入参考的分频信号与VCO反馈的分频信号,在PFD里鉴相的结果,通过连续结果时钟周期检测到鉴相的脉宽小于某值,作为锁定的有效判决规则。这种检测方式,判决方式简单,判断的结果只有锁定和非锁定两

2018-03-14 16:37

美国国家标准与技术研究院的研究人员开发出一种新颖的方法,可制成“超光速”脉冲光,在某种意义上,它们的传播速度比光更快

2012-05-08 09:46

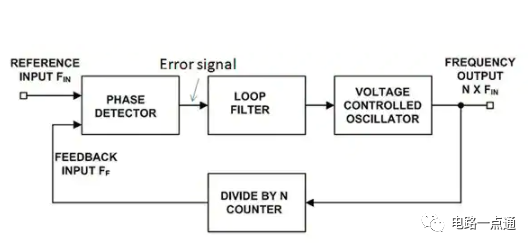

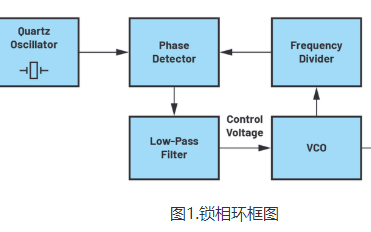

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-10-06 14:43

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

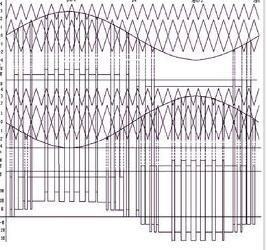

SPWM(Sinusoidal PWM)法是一种比较成熟的,目前使用较广泛的PWM法。前面提到的采样控制理论中的一个重要结论:冲量相等而形状不同的窄脉冲加在具有惯性的环节上时,其效果基本相同。

2018-02-26 15:54

涡流是这样形成的,就是质量差的夕钢片,也没有经过绝缘处理,甚至是普通铁片,可以説是个纯铁块,绕上一定数量线啳,所谓是变压器,这种变压器通上交流电源,由于交变磁场不断运动,因此不接负载铁芯(线啳)也会发热,产生这种发热情况称为涡流热量。所以涡流是不能修复的,完全是电机和变压器铁芯质量问题。仅供参考。

2019-10-07 14:53