典型高速系统应用框图举例

2018-03-16 16:25

使用报警系统安装框图

2009-06-10 08:55

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,

2020-03-29 17:19

本应用报告介绍了实现 IDT 基于 PLL 的零延迟缓冲器的输入参考时钟和输出时钟之间定义的相位关系的不同方法。该报告重点介绍了 PLL 反馈环路中不同走线长度和反馈时钟输入端的电容负载对生成早期

2021-06-15 10:48

另一种红外光束系统的方框图

2009-06-10 10:13

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶

2025-06-13 16:37

本文介绍了MM912_S812主要特性, MC9S12XS系列框图和33812简化内部框图, MM912_S812详细应用框图以及小型引擎参考设计KIT912S812ECUEVM主要特性和

2018-06-07 00:00

为了表明反馈控制系统的组成以及信号的传递情况,通常把系统各个环节用框图表示,并用箭头标明各作用量的传递情况。图1是图2所示系统的

2022-11-10 14:08

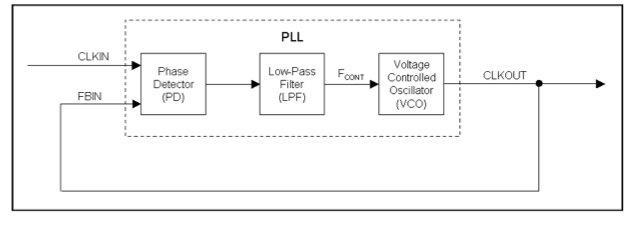

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22