波形图是显示电路电压或电流实时变化的一种图谱,由硬件电子工程师使用示波器直接测量;频谱图是显示电路射频能量在频率上的分布的图谱,由EMC工程师借助频谱分析仪测量得到——

2024-10-17 11:34

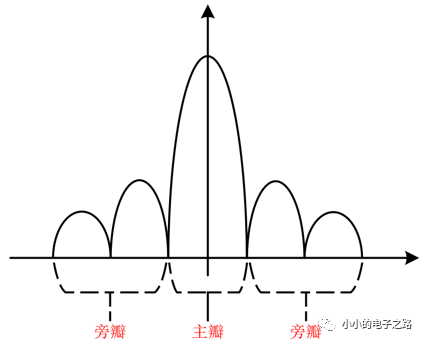

为了能既方便又明白地表示一个信号在不同频率下的幅值和相位,可以采用成为频谱图的表示方法。在傅里叶分析中,把各个分量的幅度|Fn|或 Cn 随着频率nω1的变化称为信号的幅度谱。而把各个分量的相位 φn 随角频率 nω1 变化称为信号的相位谱。

2016-09-18 18:17

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

频谱分析仪是微电子测量领域中最基础、最重要的测量仪器之一,是从事各种电子产品研发、生产、检验的重要工具。高分辨率、宽频带数字频谱分析的方法和实现一直是该领域的研究热点[1]。现代频谱分析仪是基于现代

2018-01-18 09:55

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

在数字信号处理领域,快速傅里叶变换(FFT)可以说是其核心内容之一。在利用FFT分析信号频谱的过程中,不可避免地会出现频谱泄漏现象,因此,我们所观察到的信号频谱只是其真实频谱

2023-11-03 18:08

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL在实际应用中的关键注意事项,帮助工程师规避常见设

2025-06-13 16:37

传统的频谱感知协助数据库更新频谱信息需消耗大量能量和额外频谱资源,同时在无感知基础设施依托的陌生地域难以发挥作用。泛在部署的频谱用户本身是一个接收感知单元,能够掌握实时

2023-10-17 15:08