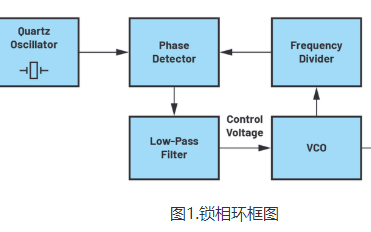

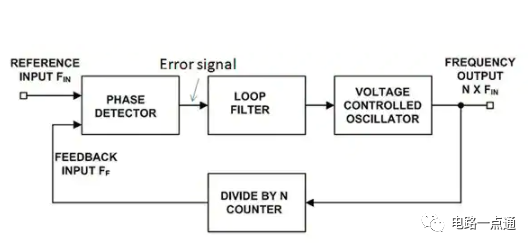

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2020-10-06 14:43

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的

2023-07-10 10:22

设备在内的许多 RF 设备项目中都可以找到 PLL。根据其具体实现,它可以服务于近直流到 GHz 和更高的频率,在系统和电路中发挥许多关键作用。

2023-07-10 09:57

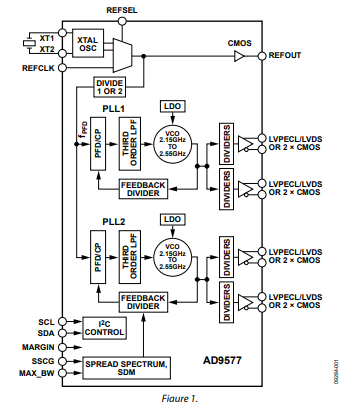

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合

2025-04-10 15:29

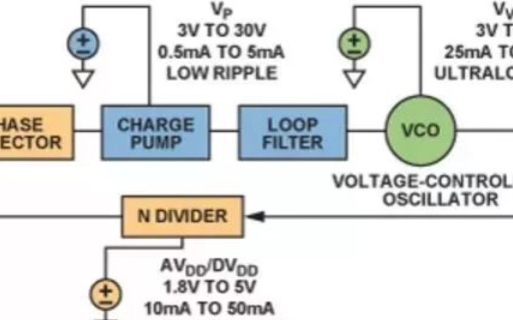

锁相环(PLL)是现代通信系统的基本构建模块,通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数模转换的时钟源。

2022-03-04 14:45

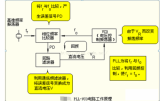

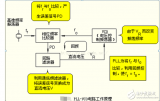

锁相环(phase locked loop),顾名思义,就是锁定相位的环路。学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出

2018-02-21 11:43

锁相环 (phase locked loop),顾名思义,就是锁定相位的环路。学过自动控制原理的人都知道,这是一种典型的反馈控制电路,利用外部输入的参考信号控制环路内部振荡信号的频率和相位,实现输出

2017-12-13 16:26

锁相环(PLL)电路是由压控振荡器(VCO)和鉴相器组成的反馈系统,振荡器信号跟踪施加的频率或相位调制信号是否具有正确的频率和相位。需要从固定低频率信号生成稳定的高输出频率时,或者需要频率快速变化时,都可以使用PLL

2022-06-13 16:14

在许多电子项目中,自动开关功能是一个常见的需求。555定时器因其简单、灵活和成本效益而成为实现这一功能的理想选择。 555定时器简介 555定时器是一种8引脚的集成电路

2024-11-12 11:02

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL

2025-06-13 16:37