通常FPGA中会有各种资源可以使用,而每种资源都需要有电源电压支持。在单片机中,通常是使用同样的电源电压供电的,比如常见的5V、3.3V。而在FPGA中,一般需要:核心电压、I/O口

2024-05-22 18:42

模拟PLL,模拟PLL是什么意思 所谓模拟PLL,就是说数字PLL中的各个模块的实现都是以模拟器件来实现的,是一个模拟

2010-03-23 10:52

数字PLL,什么是数字PLL 数字PLL PLL的概念 我们所说的PLL,其实就是锁相环路,简称为锁相环。许多

2010-03-23 10:50

本文描述电源噪声可能对RFIC 性能造成的影响。本例子的集成锁相环(PLL)和电压控制振荡器(VCO)的ADRF6820 正交解调器,所得结果也适用于其他高性能 RFIC。回复本帖查看隐藏下载链接:[hide][/hide]

2022-07-05 16:04

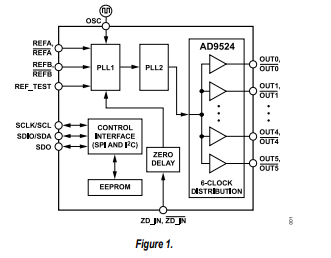

AD9524提供低功耗、多路输出时钟分配功能,具有低抖动性能,还配有片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为3.6 GHz至4.0 GHz。

2025-04-10 15:57

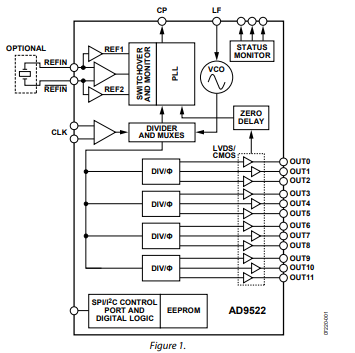

AD9522-1提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.27 GHz至2.65 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:34

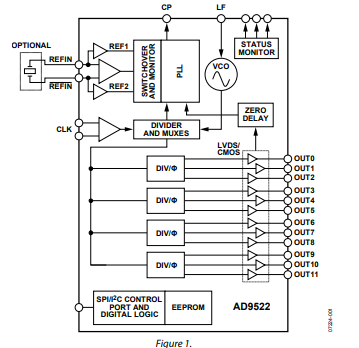

AD9522-3提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.72 GHz至2.25 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 11:50

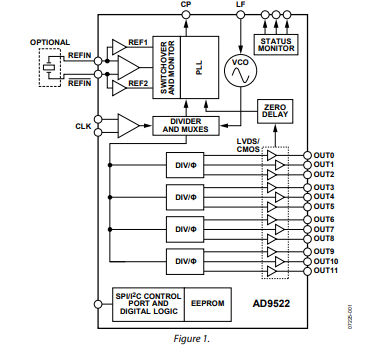

AD9522-4提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.4 GHz至1.8 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:14

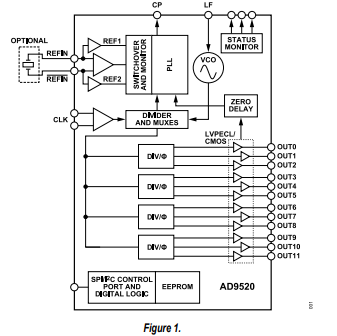

AD9520-2提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为2.02 GHz至2.335 GHz。也可以使用最高2.4 GHz的外部3.3 V/5 V VCO/VCXO。

2025-04-11 14:38

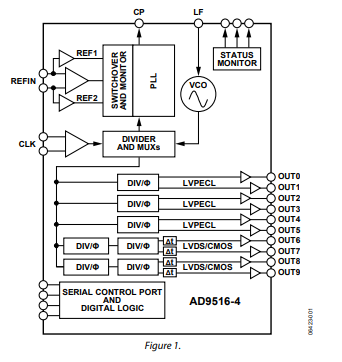

AD9516-4*提供多路输出时钟分配功能,具有亚皮秒级抖动性能,并且片内集成锁相环(PLL)和电压控制振荡器(VCO)。片内VCO的调谐频率范围为1.45 GHz至1.80 GHz。也可以使用最高2.4 GHz的外部VCO/VCXO。

2025-04-11 16:36