普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

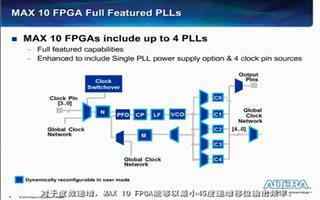

MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引脚数量也可以加倍,用作通用IO引脚。并且采用动态

2018-06-20 08:00

SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52

安森美半导体(ONSemiconductor)推出NB4N507A全集成锁相环(PLL)IC系列中的首个器件,该系列专为替代昂贵的晶振而设计,以在各种消费和网络应用中产生时钟。安森美半导体

2010-06-02 18:20

PLL时钟电路芯片最主要的特点是能使频率稳定度高,尤其是相位噪声低,优点是使用灵活且易于控制,因此对于现代电子系统来说,为了能实现更稳定的频率、更小的频差,在许多情况下都会采用时钟电路芯片。

2023-04-24 12:28

伴随着通信市场的飞速发展,用于时钟分配的复杂树状结构得到了广泛的运用。为了给许多被时钟分配及其他设计用来传送数据(通过众多具有数字时域精度的不同功能设计组合单元)的节点馈送信号,时钟树是必需的。由于

2006-03-11 13:17

调用MMCU产生时钟,输入时钟频率为100M,产生100M、50M、12.5M时钟输出,MMCU核自动生成的时钟倍频数为9,即主

2023-10-07 14:35

EUVIS的CKM151模块形成稳定频率时钟。CKM151模块借助带低频率参考时钟的锁相环路 来形成高频率时钟信号。鉴频鉴相器的低频率参考时钟可以选择板载24MHz晶体

2022-12-08 13:41

根据工信部最新统计,截至2022年底我国移动通信基站总数达1083万个,其中5G基站有231万个,占全球比例超过60%。而为了实现更深更广的网路覆盖,就有了小基站的出现,它能够深入室内做弱信号和盲区的定点覆盖,并按需提供大容量、低时延、高可靠性的网络服务,其作为5G时代的增量点,在整个生态中发挥重要的作用,预计到2025年,我国将新建共600万站。 随着使用者对网络速度、覆盖范围的需求与整体市场的快速发展,推动了基站从频率、带宽、

2023-04-13 11:22

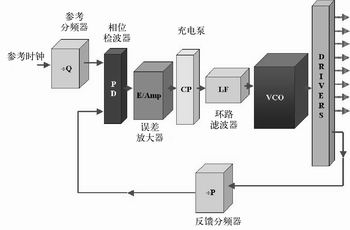

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是

2018-03-14 15:17