普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

SWM系列关于UART/CAN/PLL等时钟相关模块,计算波特率的方法。

2022-03-18 16:52

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是

2018-03-14 15:17

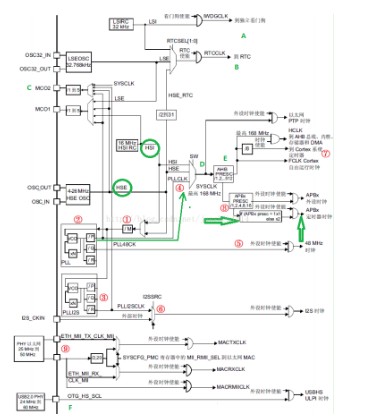

主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的倍频器出来之后的时候还需要经过一个分频系数为 P(第一个输出 PLLP)或者 Q(第二个输出 PLLQ)的分频器分频之后,最后才

2018-12-26 15:17

Spartan-6的时钟布线网络包括由BUFGMUX驱动的全局时钟网络和由I/O时钟缓冲器(BUFIO2)、PLL时钟缓

2017-02-11 08:42

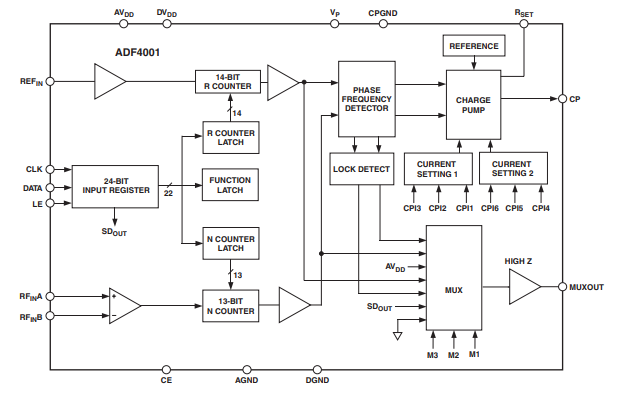

ADF4001频率合成器可用来实现要求极低噪声、稳定基准信号的PLL的时钟源。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程13位N分频器组成。此外,14位参考分频器(R

2025-04-27 10:33

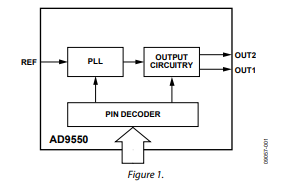

AD9550是一款基于锁相环(PLL)的时钟转换器,针对有线通信和基站应用的需求而设计。它采用整数N分频PLL来满足相关的频率转换要求。REF输入端支持单端输入参考信号。 AD9550的引脚

2025-04-10 15:43

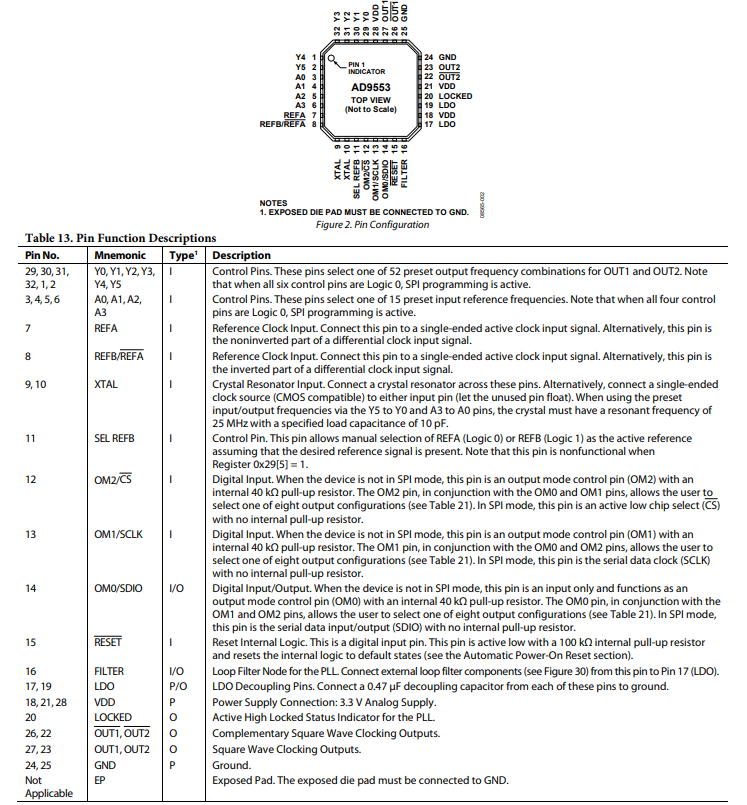

AD9553是一款基于锁相环(PLL)的时钟转换器,针对无源光纤网络(PON)和基站的需要而设计。该器件采用整数N分频PLL来支持适用的频率转换要求。用户通过REFA和REFB输入提供最多两路单端

2025-04-10 17:17

信号源分析仪是测量晶振、PLL、时钟电路、相位噪声的常用仪器。信号源分析仪作为一款综合性的测量仪器,提供了所有必需的测量能力,测量参数包括: 1)相位噪声

2019-03-14 11:53

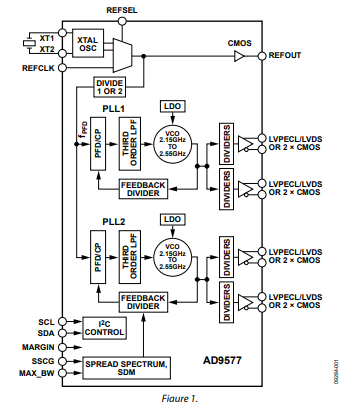

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL

2025-04-10 15:29