PLL设计和时钟频率产生机理免费下载。

2021-06-07 14:36

PLL的最大意义,就是支持任一频率变换和多路输入输出。邱文才解释道,对于通信应用来说,由于历史延续性使得接口种类众多,这是由于设备商为了节约成本,大多数都是基于固有产品

2018-06-19 09:37

普通IO可以通过BUFG再连到PLL的时钟输入上,但要修改PLL的设置 input clk的选项中要选择"No Buffer";

2017-02-09 12:54

上文XILINX FPGA IP之Clocking Wizard详解说到时钟IP的支持动态重配的,本节介绍通过DRP进行MMCM PLL的重新配置。

2023-06-12 18:24

PLL对射频输入信号有什么要求? PLL(Phase Locked Loop)是一种电路,可将输入信号和参考信号的相位和频率

2023-10-30 10:46

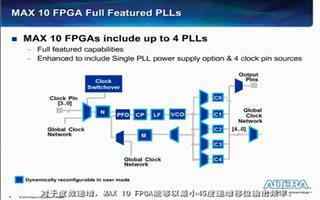

MAX 10 FPGA PLL和时钟培训,此次培训涉及到器件系列的时钟特性和选项。有20个全局时钟网络,全局CLK输入引

2018-06-20 08:00

本章节介绍了 Cyclone® IV 器件系列中具有高级特性的层次时钟网络与锁相环 (PLL),包括了实时重配置 PLL 计数器时钟

2017-11-14 10:09

pll锁定时间按照频率精度多少来计算 PLL锁定时间是指当PLL尝试将输出频率与

2023-09-02 15:12

动态配置是用户可以在 PLL 工作过程中通过专门的输入输出接口直接控制锁相环的配置参数,包括: 参考时钟分频系数(M); 反馈

2022-10-27 08:14

我们使用LMK04821芯片的单PLL模式,从OSCin输入125Mhz的差分时钟,配置参数如下。 测试中发现,输出的时钟频率

2024-11-11 06:13