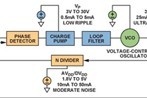

锁相环(PLL)是现代通信系统的基本构建模块PLLs通常用在无线电接收机或发射机中,主要提供"本振"(LO)功能;也可用于时钟信号分配和降噪,而且越来越多地用作高采样速率模数或数

2011-10-21 10:14

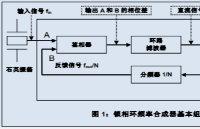

频率合成是指将高精度和高稳定度的标准信号频率通过一系列的算术运算,产生具有相同稳定度和精确度的大量离散频率的技术。锁相式频率源具有频率稳定度高、频谱纯、寄生杂波小及相位噪

2011-01-28 11:48

锁相环(Phase-Locked Loop,PLL)技术在通信领域中具有广泛的应用,其核心是一个反馈环路,通过不断比较输入信号和反馈信号的相位差来调整输出信号的频率,使其与输入信号同步。 一、PLL

2024-11-06 10:45

随着现代电子系统的不断发展,时钟管理成为影响系统性能、稳定性和电磁兼容性(EMI)的关键因素之一。在FPGA设计中,PLL因其高精度、灵活性和可编程性而得到广泛应用,本文将深入探讨PLL技术在FPGA中的动态调频与展

2025-06-20 11:51

获得高频输出的方法(第一部:锁相环电路)锁相环电路概略与爱普生产品阵容【序文】近年,伴随影像传输等普及,骨干网中流过的通信量有增无减,通信的高速、大容量化进展迅速。在这种情况下,高速化通信基础设施对高频且输出信号稳定的基准信号源的需求十分强烈。通常,从MHz频带的AT型石英晶体获得高频振荡时需要将石英片加工得很薄(理由是AT型石英晶体的频率因其厚度而定),这

2024-08-15 14:10 Piezoman压电侠 企业号

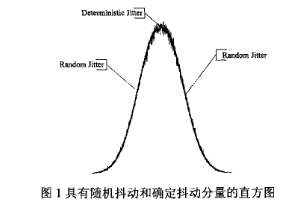

虽然系统中的自然高斯噪声发生元件始终会引发抖动但如果存在DJ则清楚地表明一个调制信号源正在向定时系统注入能量从直方图的角度来看DJ充斥于中间部分从而扩展了直方图左侧和右侧的自然高斯响应图1示出了该原理由于数字系统是有限系统就是说不应存在调幅信息而是在恰好正确的时刻获得一个0或1因此边缘布局信息的收集和分析过程正是抖动分析的切入点因为直方图是边缘的统计集合所以良好的测量需要大量的采样信息组合来获得必要的+/-6统计数据抽取这样做是有道理的由此可实现最高的测量精度

2020-05-31 07:57

射频前端模块性能关系到整个接收机的性能。本文通过对接收机进行研究,分析了超外差接收机的特点,提出了一种采用PLL技术的接收机的射频前端方案,及对射频前端的关键技术指标进行了分析。并通过软硬件平台进行

2019-03-14 16:47

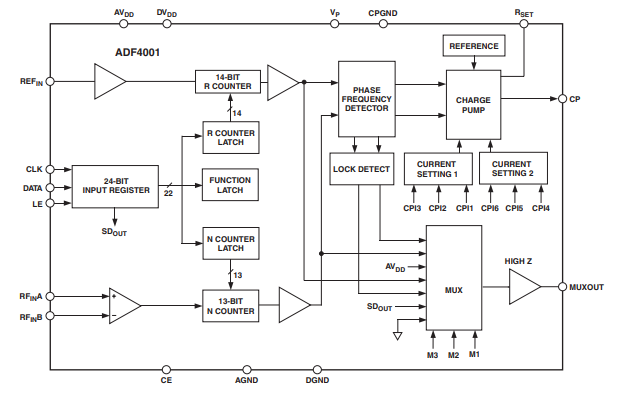

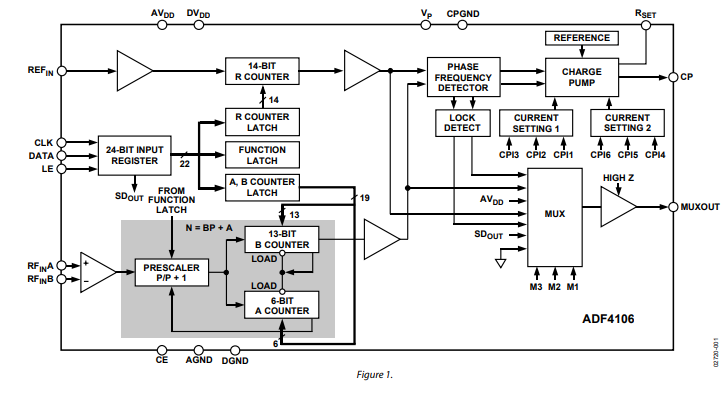

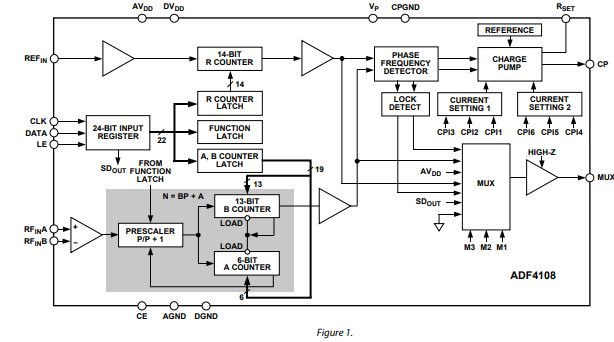

ADF4001频率合成器可用来实现要求极低噪声、稳定基准信号的PLL的时钟源。它由低噪声数字鉴频鉴相器(PFD)、精密电荷泵、可编程参考分频器和可编程13位N分频器组成。此外,14位参考分频器(R

2025-04-27 10:33

与一个外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(PLL)。其带宽极高,因此许多高频系统可以省去倍频器,从而简化系统架构并降低成本。

2025-04-27 15:55

合成器与外部环路滤波器和电压控制振荡器(VCO)一起使用,则可以实现完整的锁相环(PLL)。其带宽极高(8GHz),因此许多高频系统可以省去倍频器或预分频器,从而简化系统架构并降低成本。

2025-04-27 09:53