请教个问题:DM8168 飞加器的 PLL 参数有多少位: N(乘法器)和 P(预除法器)分别是?

2018-06-21 02:22

我们的产品要求低功耗,我现在想通过设置PLL降低主频,根据不同的使用状态使用不同的PLL分频系数,请问在程序运行中能够切换吗?怎么实现?

2020-04-21 10:08

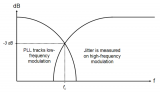

。由锁相环(PLL)跟踪到的低频率信号边缘变化不被视为抖动,因为它们被PLL有效去除。相反,没有被PLL跟踪到的高频率信号边缘变化则被测量为抖动。因此,时钟恢复方法的选择影响了

2025-06-05 19:29

@使用AD9858评估板中的DDS和PLL来实现YTO(或者叫YIG)的锁频,但是目前锁不住,我想有可能是环路滤波器的问题,照着网上的资料下载了ADI计算PLL参数的软件,发现里面可以选择的芯片

2018-09-28 15:05

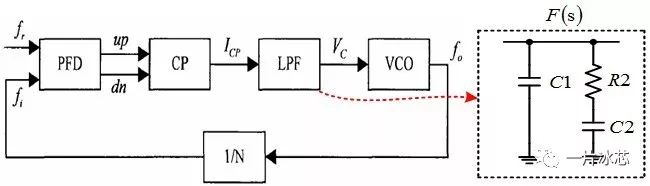

两周前有同学在qq群中讨论PLL的参数设计,之前没自己动手计算过,一直用的将PLL传递函数,忽略零点项,当做标准的二阶系统近似处理,类似ζ=0.707,wn=wc的近似吧。

2023-11-08 09:30

,输出PLLP值超过规定范围:有这个提示信息,再也不怕配置出错了。PLL的倍频和分频值有人觉得前面倍频N值很大(如下图),这样会不会出问题?答案肯定是不会。但不建议将参数N设置为最大值。特定时钟频率有些

2020-05-18 07:00

HSI为24M,用HSI配置PLL 48M时钟作为HCLK时,无法用SW口进行仿真,只要HCLK不使用PLL,就可以正常进行仿真,请教一下PLL的参数该如何配置啊?多谢

2024-03-13 09:50

1、小批量试产,有一块板卡CDCE72010开机一段时间后PLL失锁,其他9片板卡均正常。不知道这个板子发生了什么问题,如下为原理图、晶振、PLL参数 能帮忙看下,从那几个方面入手分析一下么,多谢了

2024-11-13 06:00

我正在使用Spartan-6 PLL来消除时钟抖动,我在设置VCO频率方面有很大的灵活性(通过操纵M + D值以及DCM馈送PLL的参数)。UG382,第102页,“目标是使D和M值尽可能小,同时

2019-06-20 08:45

尽管基本PLL自其出现之日起几乎保持原样,但是使用不同技术制作及满足不同应用要求的PLL的实现一直给设计者提出挑战。

2023-10-30 16:11