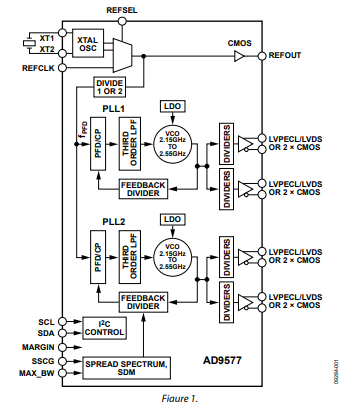

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL

2025-04-10 15:29

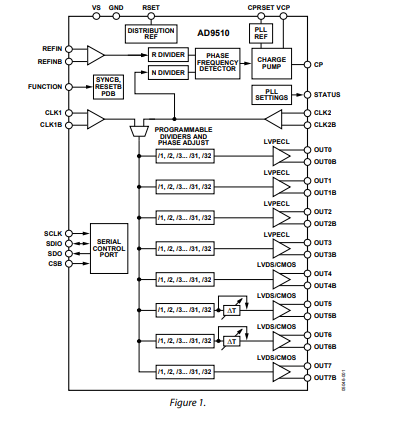

AD9510提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。4路独立的LVPECL时钟输出和4路LVDS时钟输出工作频率分别为1.2 G

2025-04-15 11:41

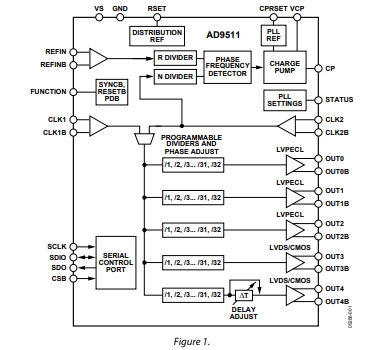

AD9511提供多路输出时钟分配功能,并集成一个片内锁相环(PLL)内核。它具有低抖动和低相位噪声特性,能够极大地提升数据转换器的时钟性能。3路独立的LVPECL时钟输出和2路LVDS时钟输出工作频率分别为1.2 G

2025-04-15 13:48

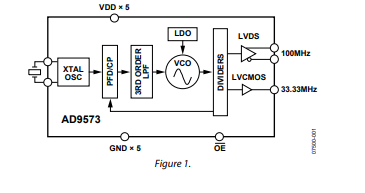

AD9573是一款高度集成的双路输出时钟发生器 , 包括一个针对PCI-e应用而优化的片内PLL内核 。 整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列 , 可实现线路卡的较高性能 。 这款器件

2025-04-11 09:51

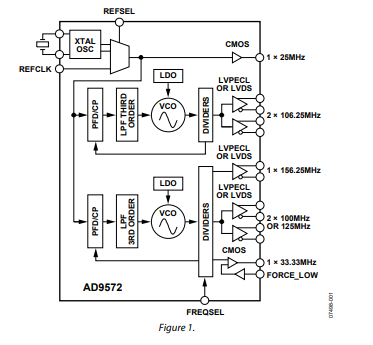

AD9572是一款多输出时钟发生器,具有两个片内PLL内核,针对包括以太网接口的光纤通道线路卡应用进行了优化。整数N分频PLL设计基于ADI公司成熟的高性能、低抖动频率合成器系列,可实现网络的较高性能。这款器件也适合

2025-04-10 17:38

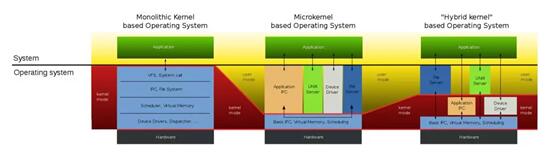

微内核设计的基本思想是简化内核功能,在内核之外的用户态尽可能多地实现系统服务,同时加入相互之间的安全保护。内核只提供最基

2019-08-14 17:20

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL

2025-06-13 16:37

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22