pll倍频最大倍数 PLL倍频是一种常见的电路设计技术,通常用于将信号的频率提高到需要的倍数。PLL

2023-09-02 14:59

据其工程师讲述:在其产品的设计中,STM32 的 HSE 外接 8MHz 的晶体产生振荡,然后通过 STM32 内部的PLL 倍频到 72MHz,作为 STM32 的系统时钟,驱动芯片工作。

2017-08-29 17:42

pll锁相环倍频的原理 PLL锁相环倍频是一种重要的时钟信号处理技术,广泛应用于数字系统、通信系统、计算机等领域,具有高可靠性、高精度、快速跟踪等优点。

2023-09-02 14:59

PLL锁相环倍频是一种用于改变输入信号频率的技术,它可以将输入信号的频率放大或缩小,以达到某种特定的目的。

2023-02-14 15:56

SWM32S 内嵌 ARM Cortex-M4 控制器,片上包含精度为 1%以内的 20MHz/40MHz 时钟,可通过 PLL 倍频到 120MHz 时钟,提供多种内置 FLASH/SRAM 大小可供选择,支持 ISP(在系统编程)操作及 IAP(在应用编程)。

2023-04-10 09:36

在时钟系统部分主要介绍时钟源选择,PLL倍频配置,时钟分发等内容。在看门狗模块部分主要介绍了开门狗复位的触发路径,看门狗模块的工作原理,CPU EndInit/Safe EndInit的实现原理等内容。

2023-02-21 13:46

有人说,芯片内部有 PLL,管它晶振频率是多少,用 PLL 倍频/分频不就可以了,那么这有回到成本的问题上来了,100M 的晶振集成到芯片里, 但我用不了那么高的频率,我只想用 10M 的频率,那我为何要去买你集成了

2023-07-28 12:24

怎么用pll电路把一个12M的频率倍频到2.4g的? PLL电路是现代电子学技术中非常重要的一种电路,它可以用来把一个低频信号转换成高频信号。PLL电路的主要作用是使用

2023-09-02 14:59

软件切换 经过PLL倍频后为系统提供输入 倍频后的PLL时钟频率可通过寄存器进行配置,可选频率为:108MHz, 120MHz, 132MHz, 144MHz, 156

2022-12-02 11:25

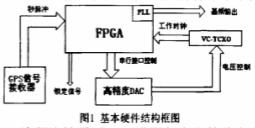

通过GPS秒脉冲信号计算标准时长,记录下这段时间内VC-TCXO产生的脉冲总数,与标准的脉冲数进行对比,最后通过DAC对VC-TCXO进行电压校正。校准后的VC-TCXO频率通过FPGA内部PLL倍频,成为发射频率。基本硬件结构框图如图 1所示。

2021-05-05 09:29