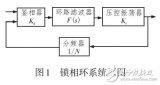

技术设计了倍频电路。首先论述了锁相环的基本原理和环路滤波器的参数设计方法,然后利用ADS软件对锁相环的环路滤波器进行了设计和仿真。最后,将设计的环路滤波器应用于实际电路,并给出了测试结果。

2017-12-07 14:46

PLL(AT16LPLL0000MP4P1G18V1A) 数据表模拟 PLL 倍频

2023-07-05 19:47

PLL(AT16LPLL0000MP4P1G18V1A) 数据表模拟 PLL 倍频

2023-03-14 19:22

STM32将HSI通过PLL倍频到64MH@[TOC](STM32将HSI通过PLL倍频到64MH)一、配置系统时钟二、打印输出系统各时钟频率三、系统初始化vSyste

2021-11-30 18:21

STM32将HSI通过PLL倍频到64MH@[TOC](STM32将HSI通过PLL倍频到64MH)一、配置系统时钟二、打印输出系统各时钟频率三、系统初始化vSyste

2021-08-10 08:07

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的

2021-08-23 09:12

)原理同样先上一张图:这次我们配置sysclk使用的是内部高速时钟 HSI。从上图时钟树可看出HSI可以直接作为SYSCLK的时钟,但是HSI最高只有8M,比较慢,我们采用的是先HSI的2分频 经过 PLL 倍频之后作为系统时钟。通常的配置是:HSI/2=4M,

2021-11-26 18:51

PLL 倍频比值 与 后分频比值 分别是什么意思?求高手指点

2013-08-05 15:09

PLL 都能实现时钟分频/倍频/输入和反馈时钟对准/多相位时钟输出功能,支持动态相位调整和 PLL 动态参数配置。

2022-10-27 07:45

网上Multisim仿真锁相环的帖子很少,本人最近经过摸索仿真了2倍及4倍频。仿真基于Multisim自带的PLL虚拟元件。参数设置是倍频成功与否的关键。

2019-09-08 15:29