pll倍频最大倍数 PLL倍频是一种常见的电路设计技术,通常用于将信号的频率提高到需要的倍数。PLL

2023-09-02 14:59

STM32的PLL 倍频后带负载能力大吗? 能带动4路CLK吗?

2024-05-17 07:47

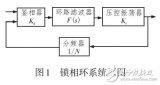

技术设计了倍频电路。首先论述了锁相环的基本原理和环路滤波器的参数设计方法,然后利用ADS软件对锁相环的环路滤波器进行了设计和仿真。最后,将设计的环路滤波器应用于实际电路,并给出了测试结果。

2017-12-07 14:46

altera EP4ce6e22c8n芯片,原来50M时钟,led灯每秒闪烁一次,按教程设置了pll倍频为100M,到板运行但效果不变,怎么回事?现在还不会仿真。

2017-07-23 22:47

原子哥,昨天用你的板调跑马灯的时候碰到一个很怪的问题。STM32RBT6的说明书上面写了SYSCLK最大的频率为72MHZ,而我们的板子晶振为8MHZ,所以PLL倍频最大只能选9。PLLMUL最大

2019-06-04 04:35

83M(想先实现PLL倍频功能,按滤波电路弄的个频率),12倍频倍到996M,SFR3[29:28]设为11,但REFCLK_OUT没输出(PLL使能设为1 了的),

2023-11-27 08:04

STM32将HSI通过PLL倍频到64MH@[TOC](STM32将HSI通过PLL倍频到64MH)一、配置系统时钟二、打印输出系统各时钟频率三、系统初始化vSyste

2021-08-10 08:07

库函数中怎么找到时钟树PLL是倍频多少或者AHB、APB分频多少现在只能看见 RCC_APB2PeriphClockCmd(RCC_APB2Periph_SYSCFG, ENABLE

2018-09-10 09:28

(想先实现PLL倍频功能,按滤波电路弄的个频率),12倍频倍到996M,SFR3[29:28]设为11,但REFCLK_OUT没输出(PLL使能设为1 了的),不知道是

2018-11-20 09:08

基于特定的开发板上的时钟策略:倍频/分频系数需要在使能 PLL 之前进行配置,所以需要在 Open PLL 之前将所有系统的时钟分频器系数以及PLL的

2021-08-23 09:12