一般在altera公司的产品上出现PLL的多,而xilinux公司的产品则更多的是DLL,开始本人也以为是两个公司的不同说法而已,后来在论坛上见到有人在问两者的不同,细看下,原来真是两个不一样的家伙。

2017-02-11 11:39

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

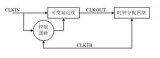

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14

cgminer是一款专业的莱特币挖矿软件,支持CPU/GPU挖矿,支持超频和调节风扇速度,非常的强大,能够帮助用户轻松的的挖得更多的莱特币,另外还对调试cgminer挖LTC莱特币与莱特币矿机哪里买进行了介绍。

2018-03-07 15:39

使用任何新技术时,生产工程师面临的最大挑战就是要测试哪些内容以及为什么要测试它们。对于现代化智能手机或平板电脑这样复杂的设备来说,这一点尤其棘手。##看到原始的测试计划时,压缩就是用来将其改进以供在Iqxstream上执行的一个合适术语。

2014-12-10 17:33

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL在实际应用中的关键注意事项,帮助工程师规避常见设

2025-06-13 16:37

线路漏电是一种很常见的安全隐患,它虽然不会立刻对人造成伤害,但长期以往会对人的健康造成不良影响,所以对于线路漏电我们要及时排查和处理。但是如何才能知道线路漏电是从哪里漏电的呢?本文将为大家介绍线路

2023-09-13 14:45

本篇文章是关于相位锁定环(PLL)频率合成器的设计和分析,重点讨论了相位噪声和频率噪声的测量、建模和仿真方法。文章以设计一个假想的PLL频率合成器为例,详细介绍了设计过程和步骤。从规格选择、电路配置

2023-10-26 15:30