软件测试女生是否合适?这种工作女生数量会比较少,一方面就是因为软件测试的工作时间长,工作强度大,另外一方面就是软件测试所需要的专业水平比较高,而女生比较少报工科以及计算机方面的专业,自然软件测试的

2018-04-24 16:30

FPGA(现场可编程门阵列)的通用语言主要是指用于描述FPGA内部逻辑结构和行为的硬件描述语言。目前,Verilog HDL和VHDL是两种最为广泛使用的FPGA编程语言。

2024-03-15 14:36

本文将通过常见的电源网络调试及PLL故障诊断等测试场景进一步描述Spectrum View的应用。

2019-09-03 08:53

该电话为用语言芯片ISD1016制作的用语音代替电话铃声留言控制器的原理电路图。该控制器可以存贮留言、音乐、一首歌或其他声响,以此替代单调的振铃声。

2014-06-12 10:34

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的PLL电路,让您对

2023-07-10 10:22

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14

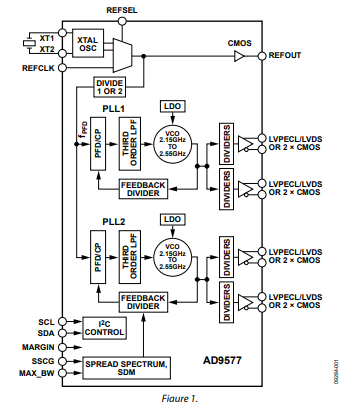

AD9577既提供一个多路输出时钟发生器功能,又带有两个片上锁相环内核PLL1和PLL2,专门针对网络时钟应用而优化。PLL设计基于ADI公司成熟的高性能、低抖动频率合

2025-04-10 15:29

在FPGA设计中,PLL(锁相环)模块作为核心时钟管理单元,通过灵活的倍频、分频和相位调整功能,为系统提供多路高精度时钟信号。它不仅解决了时序同步问题,还能有效消除时钟偏移,提升系统稳定性。本文将深入探讨智多晶PLL在实际应用中的关键注意事项,帮助工程师规避常见设

2025-06-13 16:37