本实验活动介绍锁相环(PLL)。PLL电路有一些重要的应用,例如信号调制/解调(主要是频率和相位调制)、同步、时钟和数据恢复,以及倍频和频率合成。在这项实验中,您将建立一个简单的

2023-07-10 10:22

在电子和通信领域,倍频器和锁相环(PLL)是两种常见的电路结构,它们在信号处理、频率合成和通信系统中扮演着重要角色。尽管两者在某些方面存在相似之处,但它们在功能、工作原理和应用领域等方面存在显著差异。本文将对倍频

2024-06-20 11:34

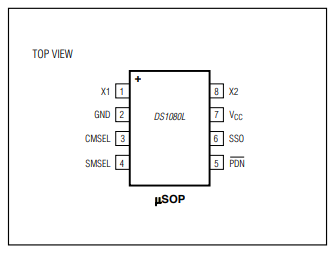

DS1080L是低抖动、基于晶振的时钟发生器,内部集成锁相环(PLL),用于产生16MHz至134MHz的扩频时钟输出。该器件的时钟倍频速率和抖动幅度可通过引脚设置。DS1080L提供扩频禁用模式和关断模式,可节省功耗。

2025-04-15 09:59

当PLL参考时钟和PLL反馈时钟的频率和相位相匹配时,PLL则被称为是锁定状态。达到锁定状态所需的时间称为锁定时间,这是PLL设计最关键的参数之一。

2018-03-14 15:17

晶振常用标称频率在1~200MHz之间。如果需要更高更稳定的输出频率,可以使用锁相环PLL将低频晶振进行倍频到1GHz以上的标称频率。锁相环PLL电路由以下几部分组成:

2023-06-21 14:01

先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位、同步释放处理,然后这个复位信号输入PLL,同时将clk也输入PLL。设计的初衷是在PLL输出有效时钟之前,系统的其他部分都保持复位状态。

2020-03-29 17:19

当涉及多倍频程放大器时,以下是一些基础知识的详解。

2023-06-15 09:58

NI Multisim 10经典教程分享--倍频器电路

2023-02-14 15:17

倍频器是指能完成输入信号频率倍增功能的电子组件,在工作频率较高而对频率稳定性要求严格的电子设备中,用一般的LC振荡器很难达到要求,若采用高稳定的晶振,通过倍频放大即可很容易的实现稳频要求。

2018-05-04 11:46

校准完成后,PLL的反馈操作使VCO锁定于正确的频率。锁定速度取决于非线性周跳行为。PLL总锁定时间包括两个部分:VCO频段校准时间和PLL周跳时间。VCO频段校准时间仅取决于PFD频率;PFD频率越高,锁定时间越短

2018-05-11 15:14