时钟网络反映了时钟从时钟引脚进入FPGA后在FPGA内部的传播路径。 报告时钟网络命令可以从以下位置运行: A,Viva

2020-11-29 09:41

PmodSF2是一个16MByte串行PCM内存模块,基于Micron P5Q PCM设计。

2019-11-28 14:46

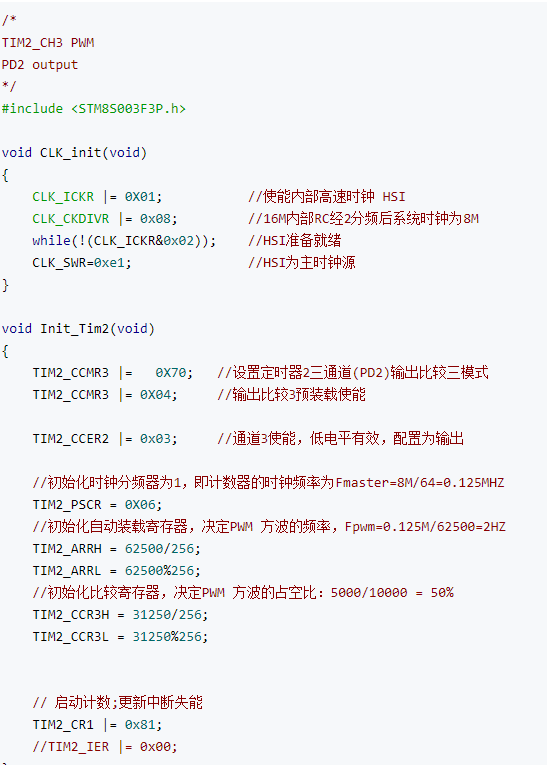

采用STM8S内部时钟(HSI);PWM模式2;占空比为50%,频率为2Hz(方便测试LED灯);PD2口外接LED灯,PD2口输出PWM波;系统时钟初始化很重要:CLK_CKDIVR |= 0x08。

2018-04-16 11:16

时钟信号在很大程度上决定了整个设计的性能和可靠性,尽量避免使用FPGA内部逻辑产生的时钟,因为它很容易导致功能或时序出现问题。内部逻辑(组合逻辑)产生的

2022-10-26 09:04

某些 PCM 设备在第一次下降之前的 PCM 时钟 (PCLK) 上升沿上参考其时序 遵循帧同步 (FS) 断言的 PCLK 边缘。本文档将此计时方法称为 帧同步参考方法。73M1866

2023-02-20 10:12

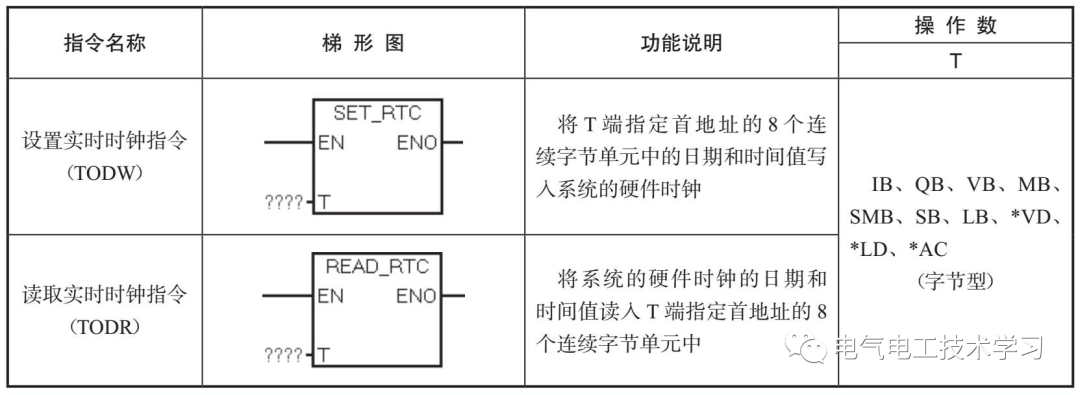

时钟指令的功能是调取系统的实时时钟和设置系统的实时时钟,它包括读取实时时钟指令和设置实时时钟指令(又称写实时

2023-12-13 13:45

STM32的时钟有两个来源——内部时钟和外部时钟。

2017-12-22 09:56

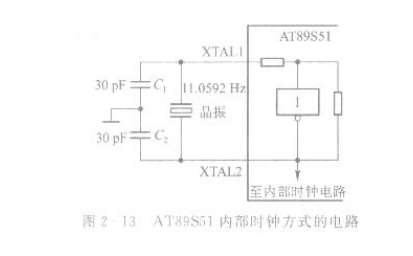

AT89S51内部有一个用于构成振荡器的高增益反相放大器,它的输入端为芯片引脚XTAL1,输出端为引脚XTAL2。这两个引脚跨接石英晶体和微调电容,构成一个稳定的自激振荡器,图2-13是AT89S51内部时钟方式的电

2019-05-07 15:50

Versal HBM 栈可通过内部 HSM0 参考时钟来进行时钟设置,此参考时钟是由 CIPS 或外部时钟源生成的。

2023-06-05 09:41