1. S参数依赖于系统阻抗 S参数的定义需要约定一个系统阻抗。同一个微波电路,在不同系统阻抗下的S参数是不同的。例如,50欧

2021-02-20 16:11

如图所示,射频部分完全抄参考设计CC2541EM_2layer,发给PCB生产厂家做50欧阻抗控制,PCB厂家计算出来的

2019-10-17 07:20

PCB设计为何一般控制50欧姆阻抗?

2020-01-15 16:17

在PCB设计中,阻抗通常是指传输线的特性阻抗,这是电磁波在导线中传输时的特性阻抗,与导线的几何形状、介质材料和导线周围环境等因素有关。 对于一般的高速数字信号传输和RF

2023-04-06 09:20

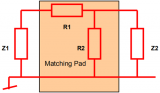

50欧的阻抗匹配电路,哪个有,参考下。

2019-09-20 09:53

。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。(2)并行阻抗

2019-01-02 10:30

。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。(2)并行阻抗

2018-11-15 20:07

。如果传输线的特征阻抗跟负载阻抗不相等(即不匹配)时,在负载端就会产生反射,造成自激振荡。PCB板内走线的低频信号直接连通即可,一般不需要加串行匹配电阻。(2)并行阻抗

2022-05-16 16:15

阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度成反比。在嵌入式系统中,一般频率大于20M的信号且PCB走线长度大于5cm时都要加串行匹配电阻,例如系统中的时钟信号、数据

2014-07-04 14:00