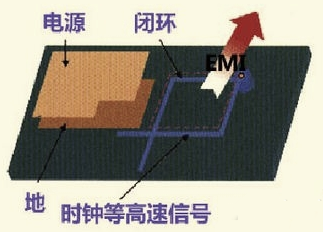

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35

MIL 认证电线或 MIL 规格电线是符合为军事应用而开发的严格标准的任何布线解决方案。与任何军用规格一样,MIL 认证的电线专为在恶劣环境中实现高性能和高可靠性而设计,这也使其成为许多非军用恶劣环境应用的有吸引力的

2023-12-04 10:25

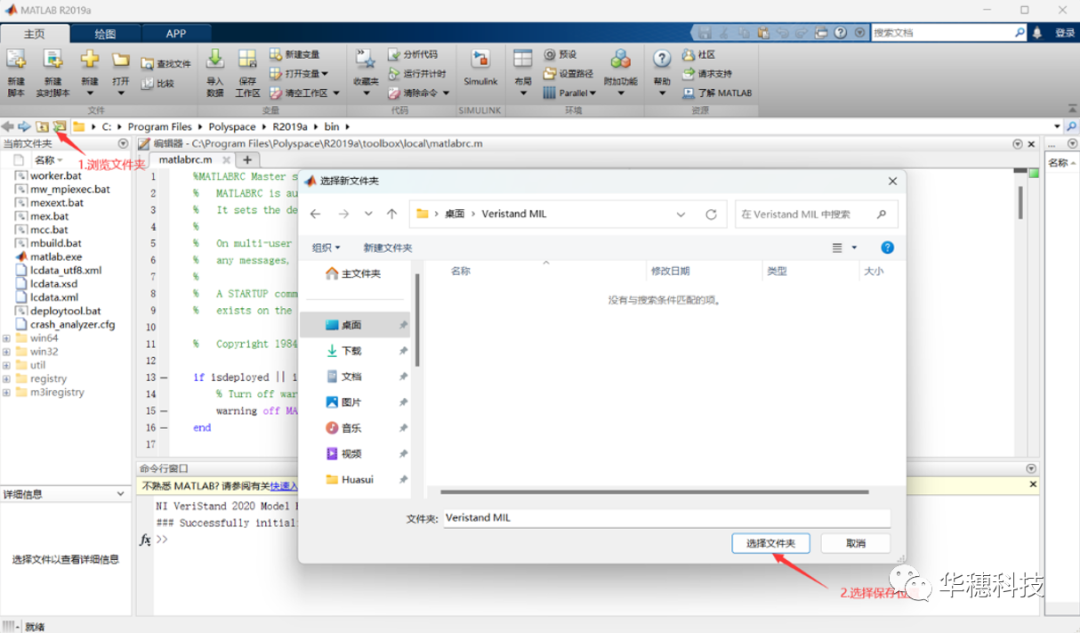

MIL(Model In The Loop)模型在环仿真测试用于在实际系统搭建完成之前进行模型测试,使用VeriStand搭建MIL测试环境,可以在不需要硬件资源的情况下测试控制模型。

2024-01-05 10:42

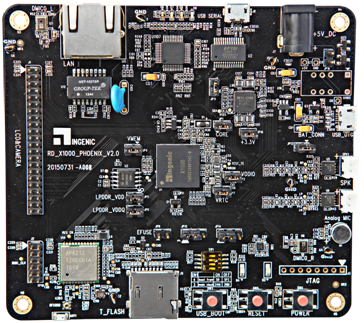

嵌入式主板 君正集成电路 X1000 Phoenix开发板 实物图

2019-11-27 17:43

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速信号线,则需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。 建议屏蔽线每1000mil打孔接地 。 高速信号的走线闭环规则 由于

2023-05-22 09:15

在PCB板上线宽及过孔的大小与所通过的电流大小的关系是怎样的? 一般的PCB的铜箔厚度为1盎司,约1.4mil的话,大致1mil线宽允许的最大电流为1A。过孔比较复杂,

2018-10-16 10:38

PCB的载流能力取决与以下因素:线宽、线厚(铜箔厚度)、容许温升。大家都知道,PCB走线越宽,载流能力越大。在此,请告诉我:假设在同等条件下,10MIL的走线能承受1A,那么50

2018-08-01 08:17

SinoV-AP1000 X86架构 Asterisk IPPBX 是一款基于开源软件asterisk 架构的IPPBX,产品采用X86架构,由传统的PC架构+asterisk card 的模式改进而来。 方便用户自

2019-11-21 15:40