电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil

2019-10-25 14:16

关于过孔盖油和过孔开窗此点(VIA和PAD的用法区分),许多客户和设计工程师在系统上下单时经常会问这是什么意思,我的文件该选哪一个选项?现就此问题点说明如下: 经常碰到这样的问题,设计严重不标准

2018-02-05 09:16

设计的线宽线距应该考虑所选PCB生产工厂的生产工艺能力,如若设计时设置线宽线距超过合作的PCB生产厂商的制程能力,轻则需要添加不必要的生产成本,重则导致设计无法生产。一般正常情况下线宽线距控制到6/

2019-10-04 16:35

一、线路 1.最小线宽: 6mil (0.153mm)。也就是说如果小于6mil线宽将不能生产,(多层板内层线宽线距最小是8MIL)如果设计条件许可,设计越大越好,线宽起大,工厂越好生产,良率越高,一般设计常规在1

2018-08-12 10:39

盲孔与通孔、盲孔与相邻的埋孔位置不能重合或相连,对同一网络要保证6mil,不同网络保证10mil以上。

2019-10-10 10:19

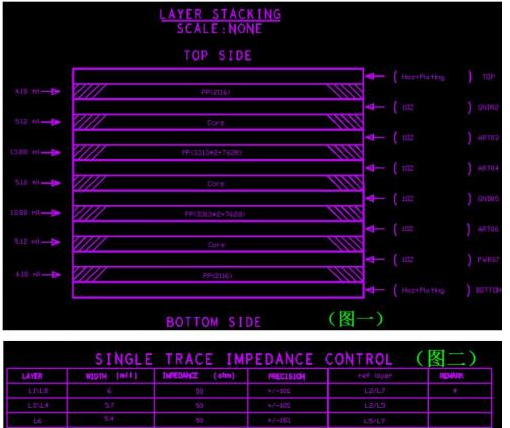

但是我们做设计时有时发现DDR器件等长没有做,其成品也可正常运行,并没产生影响,原因一般是系统软件对此信号做了延时处理,软件上做了时序控制。对于带状线来说,每1ps延时对应的走线长度是6mil左右,所以一般信号组长度每相差6mil,其总延时在1ps。

2019-03-19 17:30

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%.这有时很难做到,以FR4板材上微带线的情况

2019-09-27 15:17

PCB线路板插装元器件孔径的设计主要依据引线大小、引线成形情况及波峰焊工艺而定。在考虑工艺要求的基础上应尽量选用标准的孔径尺寸。

2019-06-13 14:15

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%.这有时很难做到,以FR4

2018-09-25 15:32

如果阻抗变化只发生一次,例如线宽从8mil变到6mil后,一直保持6mil宽度这种情况,要达到突变处信号反射噪声不超过电压摆幅的5%这一噪声预算要求,阻抗变化必须小于10%.这有时很难做到,以FR4

2019-09-14 17:24