Abstract: This application note describes using delay lines to correct system timing or "skew

2009-04-22 11:21

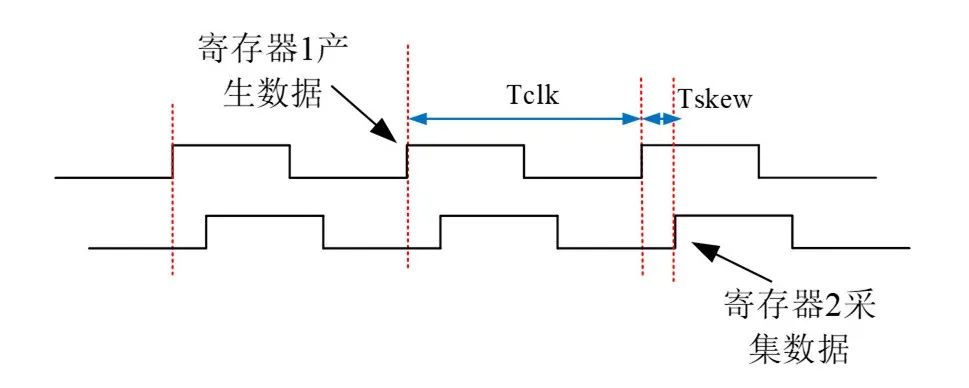

对于positive skew来说,它可以减少T的时间,相当于提升芯片的performace。但是它的hold时间会变得更加难以满足对于negative skew来说,它的hold时间更加容易满足,取而代之的是,它会降低芯片的性能。

2018-07-23 17:15

针对第2章节时序路径中用到skew,在本章再仔细讲解一下。

2023-08-14 17:50

在时序报告中,会显示出clock path skew,如果时钟偏移超过0.5ns,就需要额外关注了。

2024-03-13 09:06

为了更容易看到工具做的useful skew的效果,这里故意在下面的path上设置了很大(2.5ns)的path margin,这里是在Place阶段启用的CCD。

2022-09-30 15:57

今天要介绍的时序分析基本概念是skew,我们称为偏差。

2023-07-05 10:29

有客户反馈DIsplayport HBR测试中Interpair skew的测量项目fail得比较异常,就是固定的某条lane与其他lane之间的测试值不通过,并且偏差很大,都到几十个UI了,并且固定在某个通道,但是又没有头绪为什么。

2025-11-30 10:29

前言 本次的文章来源于Samtec首席技术专家兼总监布兰登・戈尔(Brandon Gore)博士对线缆Skew的一次深入分享探讨。 我们截取了部分讨论的重点内容。一如既往,分享给大家,希望抛砖引玉

2025-04-14 14:11

什么叫DCM(Digital Clock Management)? DCM内部是DLL(Delay Lock Loop(?)结构,对时钟偏移量的调节是通过长的延时线形成的。DCM的参数里有一个PHASESHIFT(相移),可以从0变到255。

2018-07-15 11:28

Intel 4790K的主频是4.0GHz,高通801的单核频率可达2.5GHz,A8处理器在1.2GHz,MSP430可以工作在几十MHz……这里的频率的意思都是类似的,这些处理器的频率都是厂商给定的。但是对于FPGA的工作频率而言却往往需要我们自己决定,在产品的设计初始就需要考虑FPGA工作在哪个频率,譬如250MHz。这个取值并不是瞎确定的,譬如如果定在1GHz,那显然是不可能的,有一本叫《XXXXX FPGA Data Sheet DC and Switch Characteristics》的手册给出了FPGA各个模块的直流供电特性和最高工作

2017-02-08 13:47