对于positive skew来说,它可以减少T的时间,相当于提升芯片的performace。但是它的hold时间会变得更加难以满足对于negative skew来说,它的hold时间更加容易满足,取而代之的是,它会降低芯片的性能。

2018-07-23 17:15

为了更容易看到工具做的useful skew的效果,这里故意在下面的path上设置了很大(2.5ns)的path margin,这里是在Place阶段启用的CCD。

2022-09-30 15:57

什么叫DCM(Digital Clock Management)? DCM内部是DLL(Delay Lock Loop(?)结构,对时钟偏移量的调节是通过长的延时线形成的。DCM的参数里有一个PHASESHIFT(相移),可以从0变到255。

2018-07-15 11:28

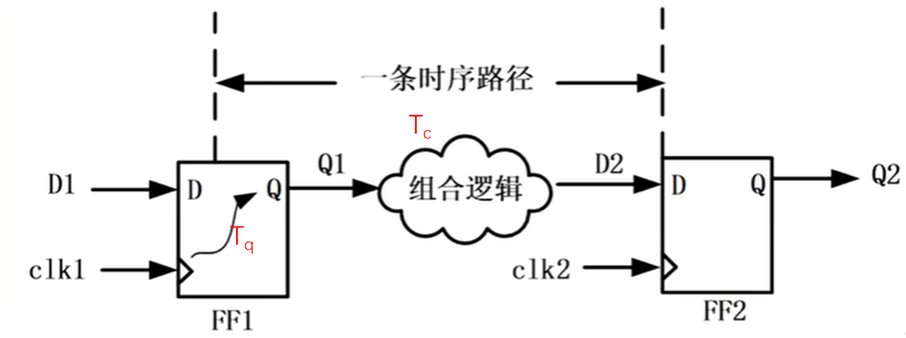

组合逻辑的延迟Tc,从FF1/CK到FF1/Q的延迟为Tq,定义Treal = Tq + Tc,从建立时间和保持时间这两个标准去考察Treal。

2023-12-01 14:55

Dc综合是基于路径,每个路径上都有Cell和net,所以基于路径的综合就是计算路径上的delay和rc(dc是使用互连线模型进行估算)。

2018-07-15 09:03

众所周知,认识和控制差分skew的来源对信号完整性至关重要,并可以有效降低产品发生终端失效的风险。

2023-06-29 15:50

本文详细介绍什么是pcb打样,对pcb打样是什么意思作全面的讲解,对您全面了解pcb打样加工有帮助。

2014-04-22 22:32

PCB拼板是PCB厂经常要做的事情,进行拼板需要注意哪些事项?PCB拼板有哪些要则?

2019-05-31 09:36

同步电路需要一种计时机制来保持有序和周期性的时序逻辑流。在数字电子学中,这种计时机制被称为时钟,简单来说,它是一个具有恒定频率的方波。

2022-10-24 10:03

在电子行业有一个关键的部件叫做PCB(printed circuit board,印刷电路板)。这是一个太基础的部件,导致很多人都很难解释到底什么是PCB。这篇文章将会详细解释PCB的构成,以及在

2017-04-25 11:38