-CID设计师 拥有十几年的高速PCB设计与SI/PI仿真经验,精通Cadence Allegro、Mentor EE、PADS-Power PCB;以及Sigrity

2018-08-07 16:15

在高速数字设计和高速通信系统中,多层PCB板被广泛采用以实现高密度、高性能的电路布局。然而,随着信号速度和密度的增加,信号完整性(SI)和电源完整性(PI)问题变得越来越突出。有效的

2025-05-15 17:39

Cadence PCB SI分析特性阻抗变化因素教程 Cadence 的PCB SI工具是一个强大的SI分析软件,下面

2010-03-21 18:37

,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。

2018-05-22 07:18

PCB Layout and SI设计问答集锦 1.如何实现高速时钟信号的差分布线? 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只

2009-04-15 00:23

在Allegro SI的参数设置环境中你可以针对不同pcb设计要求规定不同的约束条件。这些不同的约束条件可以通过参数分配表分配给电路板上不同的特定区域

2012-06-26 15:26

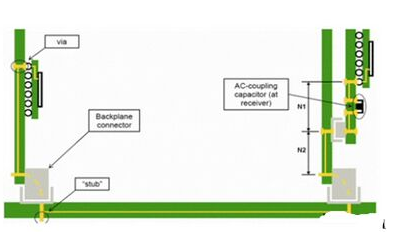

SI问题最常见的是反射,我们知道PCB传输线有“特征阻抗”属性,当互连链路中不同部分的“特征阻抗”不匹配时,就会出现反射现象。

2019-10-13 14:23

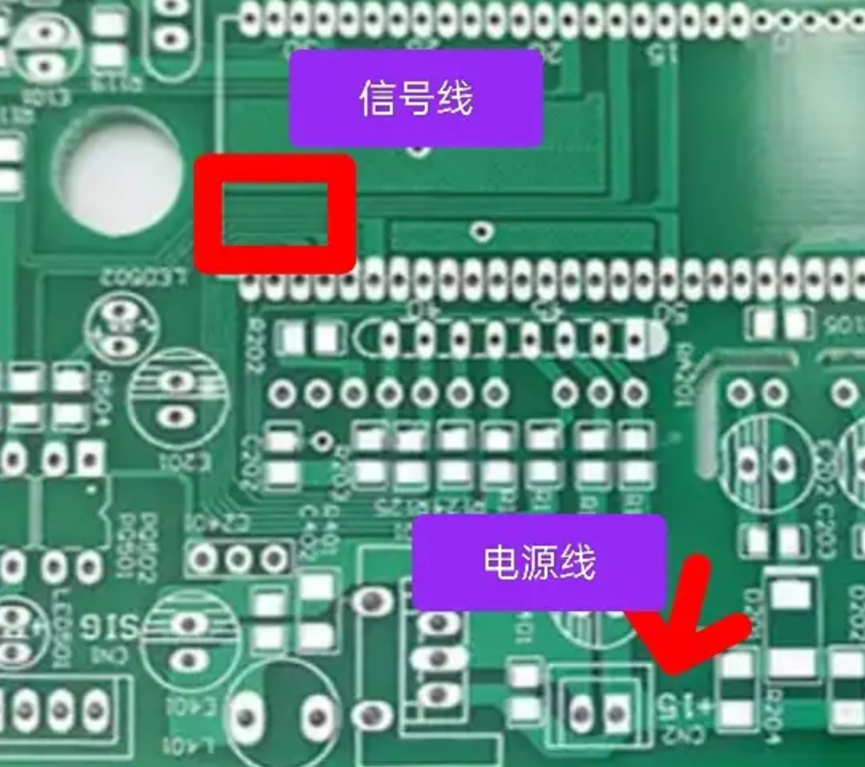

在整理SI资料之前,先整理一些基本的PCB概念的东西,帮助后面更好的理解。

2024-05-21 15:19

目前用户最需要是一个时序分析和SI结合一体工具,而且界面要优化,设置要简单,同时需要包括Design KIT。ICX Tau如果能够象Quantum-SI一样性能得到改进,那么将

2010-10-26 15:46