信号通过信道传输时会发生降级。高速信号特别容易降级,因为损耗和失真往往与频率有关。

2019-09-10 17:38

PCB Layout and SI设计问答集锦 1.如何实现高速时钟信号的差分布线? 在高速设计中,如何解决信号的完整性问题?差分布线方式是如何实现的?对于只

2009-04-15 00:23

Cadence PCB SI分析特性阻抗变化因素教程 Cadence 的PCB SI工具是一个强大的SI分析软件,下面

2010-03-21 18:37

GHz速率级别的信号算高速? 传统的SI理论对于高速信号有经典的定义。 SI:Signal Integrity ,即信号

2019-11-05 11:27

之前在设计板卡时,只是听过相关的概念,但是未真正去研究关于SI相关的知识。将之前看过的一些资料整理如下: 1 信号完整性分析 与SI有关的因素:反射,串扰,辐射。反射是由于传输路径上的阻抗不匹配导致

2021-07-27 10:10

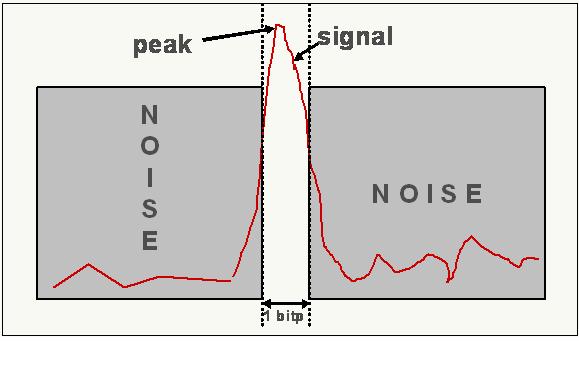

SI问题最常见的是反射,我们知道PCB传输线有特征阻抗属性,当互连链路中不同部分的特征阻抗不匹配时,就会出现反射现象。SI反射问题在信号波形上的表征就是:上冲/下冲/振

2016-11-05 02:28

渗入,手机、平板电脑的速率也很有可能达到5G、10G。SI/EMC(信号完整性/电磁兼容)问题正成为许多PCB工程师难以逾越的沟壑。机不可失,时不再来。PCB厂商都想抢

2020-09-15 10:02

在pcb layout中必须要考虑SI差的信号完整性不是由某一因素导致的,而是由板级设计中多种因素共同引起的

2011-11-21 13:57

信号完整性(Signal Integrity,SI)是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传输到接收端,我们就称该

2023-09-28 11:27

,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。

2018-05-22 07:18