本文主要分析一下在高速PCB设计中,高速信号与高速PCB设计存在一些理解

2019-11-05 11:27

本文结合实际测试中遇到的时钟信号回沟问题介绍了高速信号的概念,进一步阐述了高速信

2022-09-14 09:20

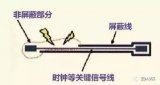

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建

2019-05-06 18:08

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速

2023-05-22 09:15

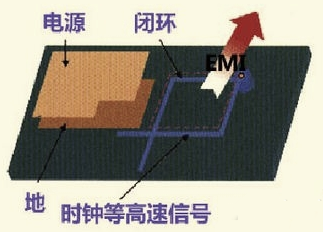

所有的高速信号必须有良好的回流路径,尽可能地保证时钟等高速信号的回流路径最小,否则会极大的增加辐射,并且辐射的大小和

2019-04-03 09:30

在高速PCB设计中,“信号”始终是工程师无法绕开的一个知识点。不管是在设计环节,还是在测试环节,信号质量都值得关注。在本文中,我们主要来了解下影响

2019-10-10 17:21

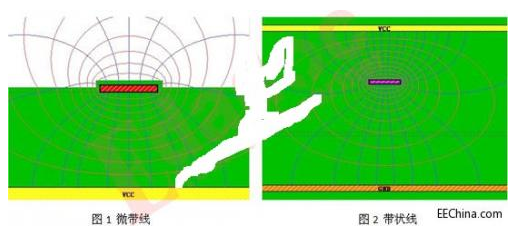

随着信号工作频率的不断提高,信号完整性问题已经成为高速PCB工程师关注的焦点,什么是差分信号? 通俗地说,就是驱动端发送

2011-11-21 13:45

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建

2017-08-25 15:35

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据

2019-09-20 14:12