几乎所有的芯片设计、芯片验证工程师,每天都在和VCS打交道,但是由于验证环境的统一化管理,一般将不同的编译仿真选项集成在一个文件里,只需要一两个人维护即可。所以大部分人比较少有机会去深入地学习VCS的仿真flow。基于此,本文将介绍VCS仿真的 两种flow ,概

2023-01-10 11:20

AMD Alveo 加速卡使用有两种流程,AMD Vitis Software Platform flow 和 AMD Vivado Design Tool flow。比较常见的是 Vitis

2024-11-13 10:14

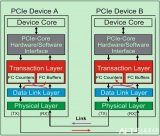

PCIe Spec规定,PCIe设备的每一个端口(Ports)都必须支持Flow Control机制,在发送TLP之前,Flow Control必须先检查接收端口是否有足够的Buffer空间来接

2018-05-24 09:26

在 AMD Vivado Design Suite 2024.2 版本中,Advanced Flow 自动为所有 AMD Versal 自适应 SoC 器件启用。请注意,Advanced Flow

2025-01-23 09:33

在最新发布的 AMD Vivado Design Suite 2024.2 中,引入的新特性之一是启用了仅适用于 AMD Versal 自适应 SoC 器件的 Advanced Flow 布局布线

2025-01-17 10:09

PCIe总线为了解决这一问题,提出了Flow Control的概念,如下图所示。PCIe总线中要求接收方必须经常(在特定时间)向发送方报告其VC Buffer的使用情况。而报告的方式是,接收方向发送

2018-04-26 08:54

Optical Flow SDK 展示了 Turing GPU 和 Ampere GPU 的最新硬件功能,该功能专用于计算图像之间像素的相对运动。该硬件使用复杂算法来生成高度精确的流向量,这些向量对于帧到帧的强度变化具有鲁棒性,并可追踪真实的物体运动。

2022-09-13 15:21

在处理TLP报文时,根据Fmt字段以及Type字段可以将TLP报文分为二十多种,当TLP报文送至数据链路层时,数据链路层在进行流量控制处理时则不会考虑这么多种情况。数据链路层里面的Flow Control,则会将报文分为三类:

2023-07-03 09:20

由于VC0是默认使能的,所以当Flow Control初始化开始时,其会被自动的初始化。其他的Virtual Channel是可选的,只有当被配置为使能的时候才会被初始化。

2018-05-24 09:18

、System Verilog、VHDL、System C等。在我们的教程中用的是Verilog这种硬件描述语言(HDL),做过PCB设计的同学肯定会觉得这个过程很类似绘制原理图;

2018-12-20 13:46