DDR3内存已经被广泛地使用,专业的PCB设计工程师会不可避免地会使用它来设计电路板。本文为您提出了一些关于DDR3信号正确扇出和走线的建议,这些建议同样也适用于高密度

2018-06-16 07:17

本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

PCB设计实现,对PCB板工艺也提出更高要求,经过与PCB厂的沟通,并结合EDA软件的使用,按照信号完整性要求去控制走线的阻抗。

2019-10-04 17:17

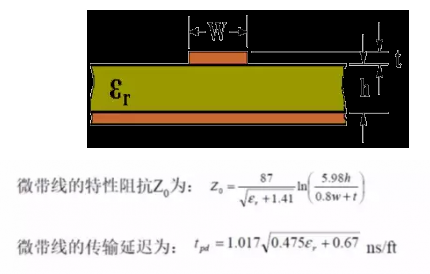

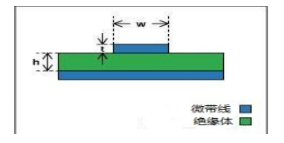

PCB中的信号线分为两种,一种是微带线,一种是带状线。 微带线,是走在表面层(microstrip),附在

2020-09-30 10:38

DDR5标准JESD79-5文件中没有明确的控制阻抗建议,DDR4时代基本内存条上时钟阻抗还是跟着芯片、主板走的70-80欧姆。线宽相对而言比较细。不知道你开始使用DDR5没有,你有关注过

2024-07-16 17:47

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚至 4 次,而随着芯片运行

2020-11-22 11:54

在普通印制电路板的布线中由于信号是低速信号,所以在3W原则的基本布线规则下按照信号的流向将其连接起来,一般都不会出现问题。但是如果信号是100M以上的速度时,布线就很有讲究了。由于最近布过速度高达300M的DDR信号,所以仔细说明一下DDR信号的布线原则和技巧。

2019-03-24 10:00

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径),最常见的传输线也就是我们PCB板上的走

2020-11-06 10:25

电路布局。为了有效地减少EMI,最好把信号线和地线的过孔分开。此外,选择合适的过孔类型可以大大提高PCB的可靠性和性能。

2023-08-26 12:06

很多人对于PCB走线的参考平面感到迷惑,经常有人问:对于内层走线,如果走线一侧是VCC,另一侧是GND,那么哪个是参考平面?

2018-03-08 17:18