请教各位,在实际工程中,DDR地址线分组需要同组同层吗? 是不是只有数据组才考虑同组同层,地址线分组可以不用同组同层?因为它的传输速率没有数据组的高?

2024-11-19 14:20

电子发烧友网为你提供DDR 高速PCB 设计走线绕等长资料下载的电子资料下载,更有其他相关的电路图、源代码、课件教程、中文资料、英文资料、参考设计、用户指南、解决方案等资料,希望可以帮助到广大的电子工程师们。

2021-03-30 08:42

[size=14.3999996185303px]我有个ARM的板子,DDR2和NAND的数据线是复用的,这样PCB走线的时候,除了原来

2016-10-10 17:09

在高速PCB设计中,DDR模块是绝对绕不过去的一关。无论你用的是DDR、DDR2还是DDR3,只要设计不规范,后果就是—

2025-04-29 13:51

由于FPGA芯片是有关于DDR的设计指导文档,我司的PCB工程师和客户在投板前也反复确认了该DDR模块的设计是完全按照文档上面每一条细致的指导去布线的。

2021-03-17 15:00

PCB的DDR4布线指南和PCB的架构改进

2023-12-07 15:15

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计

2023-08-24 08:40

上期和大家聊的电源PCB设计的重要性,那本篇内容小编则给大家讲讲存储器的PCB设计建议,同样还是以大家最为熟悉的RK3588为例,详细介绍一下DDR模块电路的PCB设计

2023-08-21 17:16

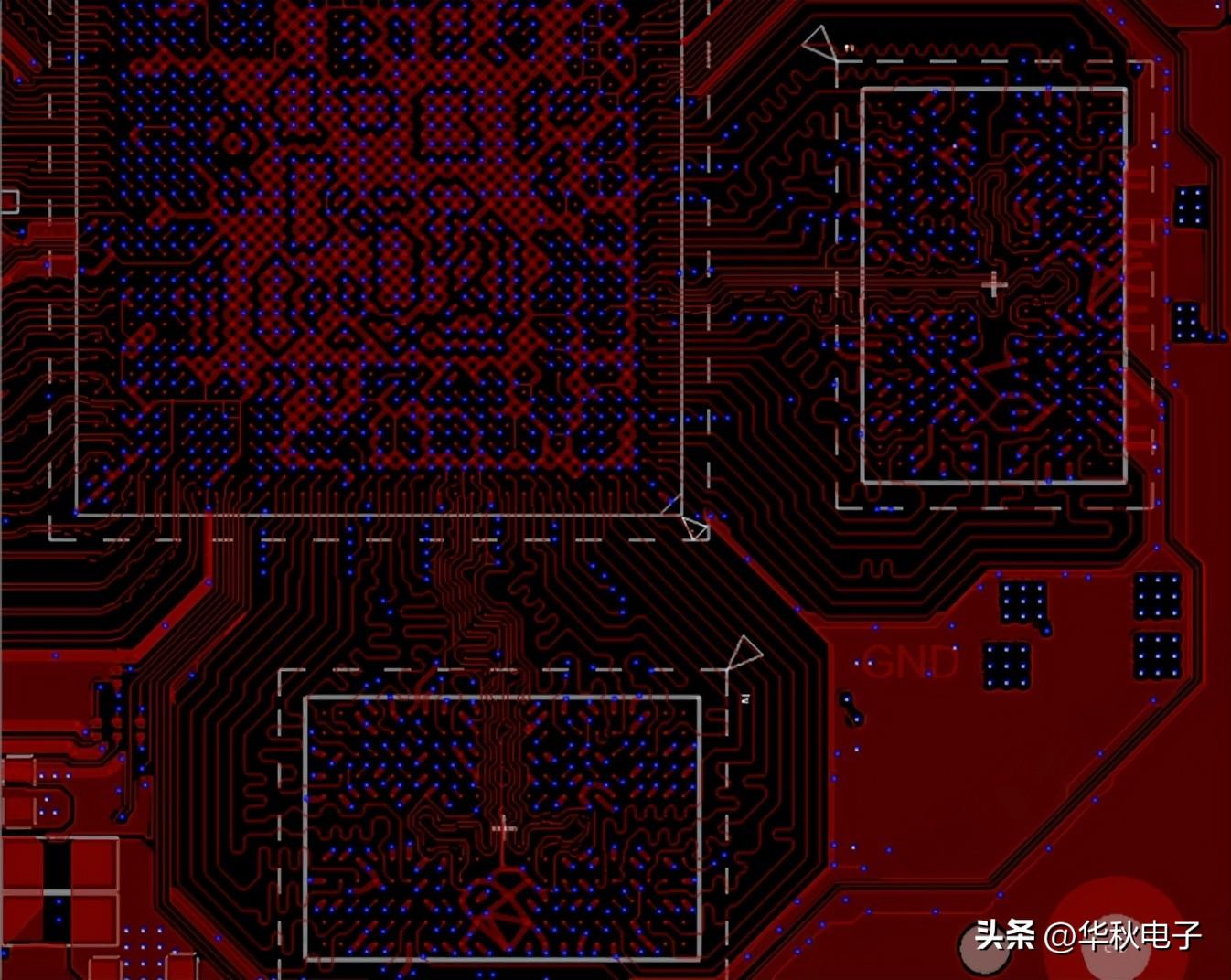

PCB设计空间足够的情况下,优先考虑留出DDR电路模块所需要的布局布线空间,拷贝瑞芯微原厂提供的DDR模板,包含芯片与DDR颗粒相对位置、电源滤波电容位置、铺铜间距等完

2023-08-18 10:55