本文主要使用了Cadence公司的时域分析工具对DDR3设计进行量化分析,介绍了影响信号完整性的主要因素对DDR3进行时序分析,通过分析结果进行改进及优化设计,提升信号质量使其可靠性和安全性大大提高。##时序分析。##PCB

2014-07-24 11:11

选择PCB板材必须在满足设计需求和可量产性及成本中间取得平衡点。设计需求包含电气和机构这两部分。通常在设计非常高速的PCB板子(大于GHz的频率)时这材质问题会比较重要。

2019-06-03 14:46

本文章主要涉及到对DDR2和DDR3在设计印制线路板(PCB)时,考虑信号完整性和电源完整性的设计事项,这些是具有相当大的挑战性的。文章重点是讨论在尽可能少的PCB层数

2018-02-06 18:47

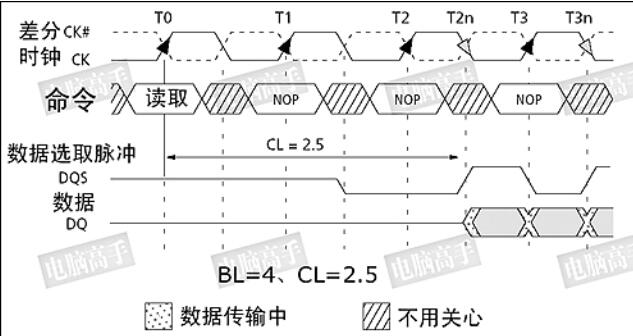

突发长度,由于DDR3的预期为8bit,所以突发传输周期(BL,Burst Length)也固定位8,而对于DDR2和早期的DDR架构的系统,BL=4也是常用的,DDR

2018-06-21 09:20

DDR是Double Data Rate的缩写,即“双倍速率同步动态随机存储器”。DDR是一种技术,中国大陆工程师习惯用DDR称呼用了DDR技术的SDRAM,而在中国台

2023-07-16 15:27

DDR=Double Data Rate双倍速率同步动态随机存储器。严格的说DDR应该叫DDR SDRAM,人们习惯称为DDR,其中,SDRAM 是Synchronou

2018-05-23 16:07

DDR应用案例

2024-04-07 14:36

DDR 代表双倍数据速率double data rate,GDDR 代表图形双倍数据速率graphics double data rate。

2024-03-17 09:24

从那时起,采用DDR2、甚至最新的DDR3 SDRAM的新设计让DDR SDRAM技术黯然失色。DDR内存主要以IC或模块的形式出现。如今,

2011-07-11 11:17

嵌入式 DDR(Double Data Rate,双数据速率)设计是含DDR的 嵌入式 硬件设计中最重要和最核心的部分。随着嵌入式系统的处理能力越来越强大,实现的功能越来越多,系统的工作频率越来越高,

2018-04-11 15:33