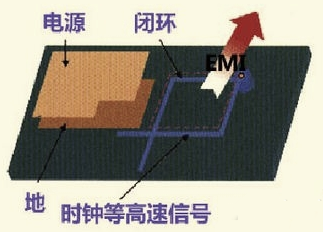

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-05-06 18:08

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速

2023-05-22 09:15

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2017-08-25 15:35

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线,每1000mil,打孔接地。

2019-03-15 14:05

IIC通信是一种双线制串行总线,由SDA(串行数据线)和SCL(串行时钟线)两条线组成。SDA线用于传输数据,而SCL线则用于传输时钟。在IIC通信中,数据的传输是由主设备发出开始信号,然后将数据发送给从设备,最后发出停止信号结束传输。

2023-08-26 12:02

在PCBLayout阶段,合理的选择一定层数的印制板尺寸,能充分利用中间层来设置屏蔽,更好地实现就近接地,并有效地降低寄生电感和缩短信号的传输长度,同时还能大幅度地降低信号的交叉干扰等,所有这些方法都对高频电路的可靠性有利。

2019-09-17 14:22

电源线尽可能的宽,不应低于18mil,信号线宽不应低于4mil,cpu出入线不应低于4mil(或6mil),线间距不低于8mil;高密度板可采用4/6mil的线宽/间距,低密度版,尽量采用6/8mil的线宽/间距。信号线间距须遵循3W原则。

2019-10-25 14:16

双层pcb板正反两面都有布线,元器件可以焊接在正面,也可以焊接在反面,双层线路板这种电路板的两面都有元器件和布线,不容质疑,设计双层PCB板的难度要高更多,下面我们来分析下双层pcb板布

2017-08-26 16:03

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高

2019-07-01 15:24

20GHz是一个比较有迷惑性的频点,在20GHz之后,我们的直角走线就变成了一个非常大的坑。至于圆弧走线和45度走线,虽然没有和直角走线那么大的区别,但是在30GHz以

2021-03-27 10:32