对于长距离传输的高速信号,尤其是背板之类的,需要特别注意损耗带来的影响,避免高频分量过多损失掉,因此在布线前期就需要规划选择一个合适的走线层。

2023-12-13 18:21

由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速

2024-01-08 15:33

过多损失掉,因此在布线前期就需要规划选择一个合适的走线层。这里我们通过仿真软件来对比表层走线与内层

2020-03-09 10:57

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高速信号线,

2020-02-14 11:53

串扰可能发生在单个PCB层上的相邻走线之间,也可能发生在两层PCB之间相

2023-10-12 09:25

本文主要详解PCB设计高速模拟输入信号走线,首先介绍了PCB设计高速模拟输入信号

2018-05-25 09:06

PCB四层板中我将中间两层设置成了信号层,能否给点实用的布线的经验???当布完线

2023-04-11 17:33

表层走线与内层走线更为规范的说法应该是微带线与带状线。两种

2020-12-19 10:23

每个层的信号线走线方向与相邻板层的走线方向要不同,最好是相邻

2019-08-29 10:41

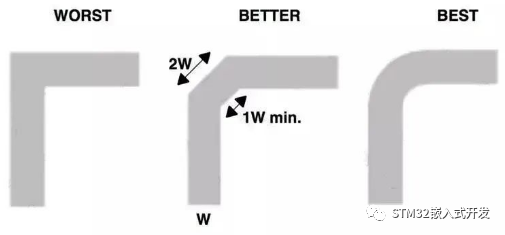

现在但凡打开SoC原厂的PCB Layout Guide,都会提及到高速信号的走线的拐角角度问题,都会说高速信号不要以直

2023-04-03 16:29