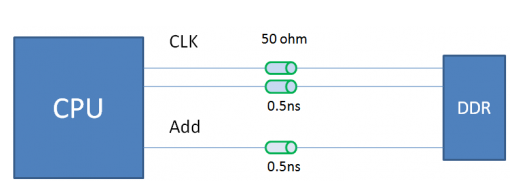

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2017-09-01 14:03

在当前的PCB 设计当中,对于走线长度的要求越来越多。Expedition PCB 自动调线的功能强大。在PCB 的设计当中若能最大限度地使用Expedition

2018-05-15 10:49

PCB布线方法在不断进步,灵活的布线技术可以缩短导线长度,释放更多的PCB空间。传统PCB布线受到导线坐标固定和缺少任意角度导线的限制。去除这些限制可以显著改善布线的质

2018-12-19 15:32

高频信号一般使用串行阻抗匹配。串行电阻的阻值为20~75Ω,阻值大小与信号频率成正比,与PCB走线宽度和长度成反比。在嵌入式系统中,一般频率大于20M的信号PCB走线长度大于5cm时都要加串行匹配电阻

2023-09-12 17:32

当电容安装在PCB板上时,就会存在一个额外的回路电感,这个电感就与电容的安装有关系。回路电感值的大小是依赖于设计的。回路电感的大小取决于电容到过孔的这段线的线宽和线长,走线的长度即连接电容和电源/地平面长度,两个孔间的距离,孔的直径,电容的焊盘,等等。

2019-09-16 11:49

图4显示了在一个PCB上输入电源(Vin)至负载(RL)的不同走线方式。为了降低滤波电容器(C)的ESL,其引线长度应尽量减短;而Vin。正极至RL和Vin负极至R1的走线应尽量靠近。

2018-06-21 09:00

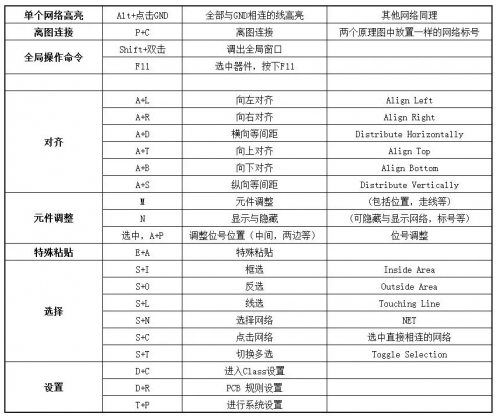

R+L 输出PCB中所有网络的布线长度 Ctrl+左键点击对正在布的线完成自动布线连接 M+G 可更改铜的形状; 按 P+T 在布线状态下,按 Shift+A 可直接进行蛇线走线 T+R 对已布完的线进行蛇线布线 E++M+C 点击空

2019-10-15 14:23

虽然通过增加走线宽度可以减少20%的自感,但减少50%走线的长度,减少50%的自感。相对而言,走线宽度必须增加5倍,以减少50%的自感。

2020-10-10 11:40

【导读】PCB 差分走线的设计中最重要的规则就是匹配线长,其它的规则都可以根据设计要求和实际应用进行灵活处理。同时为了弥补阻抗的匹配可以采用接收端差分线对之间加一匹配电阻。 其值应等于差分阻抗的值。这样信号品质会好些。

2016-12-07 01:10

根据 50 欧姆阻抗线宽进行布线,尽量从焊盘中心出线,线成直线,尽量走在表层。在需要拐弯的地方做成45 度角或圆弧走线,推荐在电容或电阻两边进行拐弯。如果遇到器件走线匹配要求的,请严 格按照datasheet上面的参考值长度走线。比如,一个放大管与电容之间的走线长度(或电感之间的走

2023-04-19 14:10