在PCB布局布线时,很多新人工程师可能会听见这种说法,类似于“PCB蛇形线越多,就显得板子高级”,虽然蛇形线可以调整长度

2024-10-15 13:56

传输线的定义是有信号回流的信号线(由两条一定长度导线组成,一条是信号传播路径,另一条是信号返回路径),最常见的传输线也就是我们P

2020-11-06 10:25

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDR SDRAM)甚

2020-11-22 11:54

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都会造成EMI的泄漏。建议屏蔽线

2019-03-15 14:05

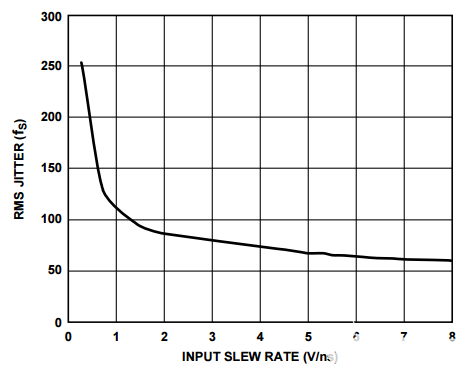

PCB走线的行为类似于低通滤波器,当时钟信号沿走线行进时会衰减,并随着走线长度的增加而增加脉冲边沿失真。较高频率的

2023-01-30 11:48

走线颈口长度大于 0.5mm 宽的走线可能通过颈口连接到 0603 的焊盘。

2018-07-05 11:35

今天我们讲一下与时钟(clock)相关的PCB的设计考虑,主要分两部分:原理图设计 - 针对时钟电路应该放置哪些器件?以及PCB布局和走

2018-11-25 11:09

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

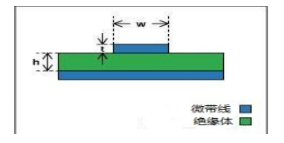

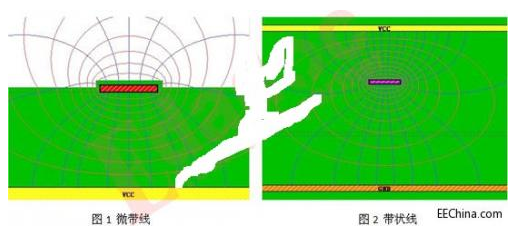

PCB中的信号线分为两种,一种是微带线,一种是带状线。 微带线,是走在表面层(microstrip),附在

2020-09-30 10:38

串行信号在发送端将数据信号和时钟(CLK)信号通过编码方式一起发送,在接收端通过时钟数据恢复(CDR)得到数据信号和时钟信号。由于时钟数据在同一个通道传播,串行信号对和

2019-09-20 14:12