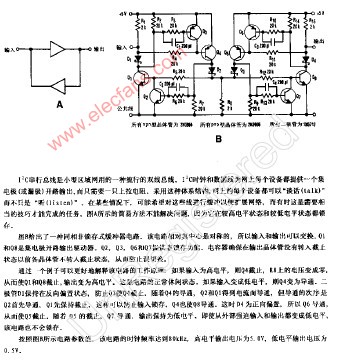

IC数据和时钟时钟线缓冲电路

2009-09-12 11:57

滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。 2 时钟线的处理 2.1)建议先走时钟线。 2.2)频率大于等于66M的

2018-09-11 16:05

一、时钟线要求 (1)时钟驱动器布局在PCB中心而非电路板外围,布局尽量靠近,走线圆滑、短,非直角、非T形,布线可选4~

2019-05-21 09:34

并且要有良好的地层,而不是靠近I/O接口处。不可将时钟产生电路做成子卡或者子板的形式,必须做在单独的时钟板上或者承载板上。如下图所示,绿色框中部分下一层最好不要走线在PCB

2015-12-20 19:27

由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速信号网络,在多层的

2024-01-08 15:33

CB上的任何一条走线在通过高频信号的情况下都会对该信号造成时延时,蛇形走线的主要作用是补偿“同一组相关”信号线中延时较小的部分,这些部分通常是没有或比其它信号少通过另外的逻辑处理;最典型的就是

2019-05-22 02:48

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果没有

2017-11-25 07:43

pcb平行走线的影响 PCB(Printed Circuit Board,印刷电路板)是电器设备中重要的组成部分,被广泛应用在电子工业和通讯工业中。 PCB设计是电路

2023-09-05 15:42

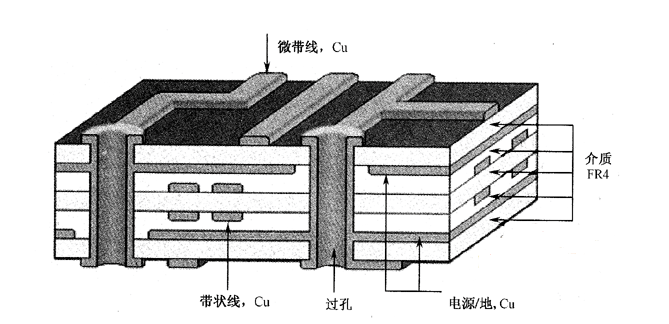

在多层PCB尤其是高速PCB中,经常将介质之间的若干个金属层(Plane)分配给电源和地(PoweriGnd)网络。这样PCB上的走线就可以大致分为两类:微带

2023-08-28 14:53

在PCB设计中,等长走线主要是针对一些高速的并行总线来讲的。 由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟周期可能要采样两次(DDRSDRAM)甚至4

2020-10-24 09:29