,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在PCB上的传输延迟的差异

2020-10-24 09:29

频率的提高,信号传输延迟对时序的影响的比重越来越大,为了保证在数据采样点(时钟的上升沿或者下降沿)能正确采集所有信号的值,就必须对信号传输的延迟进行控制。等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的

2020-11-22 11:54

对于广大PCB设计工程师而言,提到时序问题就感觉比较茫然。看到时序图,更是一头雾水,感觉时序问题特别深奥。其实在平常的设计中最常见的是各种

2012-10-22 11:51

我们俗称的 PCB 信号等长处理。等长的目标是为了满足同组信号的时序匹配要求。 2、等长范围应严格遵守不同接口或者信号的

2023-07-27 07:40

PCB设计中常见的走线等长要求

2023-11-24 14:25

1.关于等长 第一次听到“绕等长工程师”这个称号的时候,我和我的小伙伴们都惊呆了。每次在研讨会提起这个名词,很多人也都是会心一笑。 不知道从什么时候起,绕等长成了一种时尚,也成了

2021-01-20 12:11

等长走线的目的就是为了尽可能的减少所有相关信号在 PCB 上的传输延迟的差异。至于 USB/SATA/PCIE 等串行信号,并没有上述并行总线的时钟概念,其时钟是隐含在串行数据中的。数据发送方将时钟

2019-04-26 15:27

如图所示很多用户在进行等长的时候回出现直角或者锐角的等长走线。 那么怎么解决呢: 1)在直接快捷键TR进行蛇形等长的时候,可以按字母键盘上方的数字1 或者2来调整等长走

2020-10-18 09:36

时序是大家非常头痛,也觉得非常复杂的话题,所以高速先生小陈在之前的时序话题中试图用两对恋人的恋爱关系来解释时序问题,绕口令式的比喻不知道有多少人真正看懂了?

2022-02-12 15:29

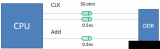

DDR布线在PCB设计中占有举足轻重的地位,设计成功的关键就是要保证系统有充足的时序裕量。要保证系统的时序,线长匹配又是一个重要的环节。我们来回顾一下,DDR布线,线长匹配的基本原则是:地址,控制

2018-03-23 10:05