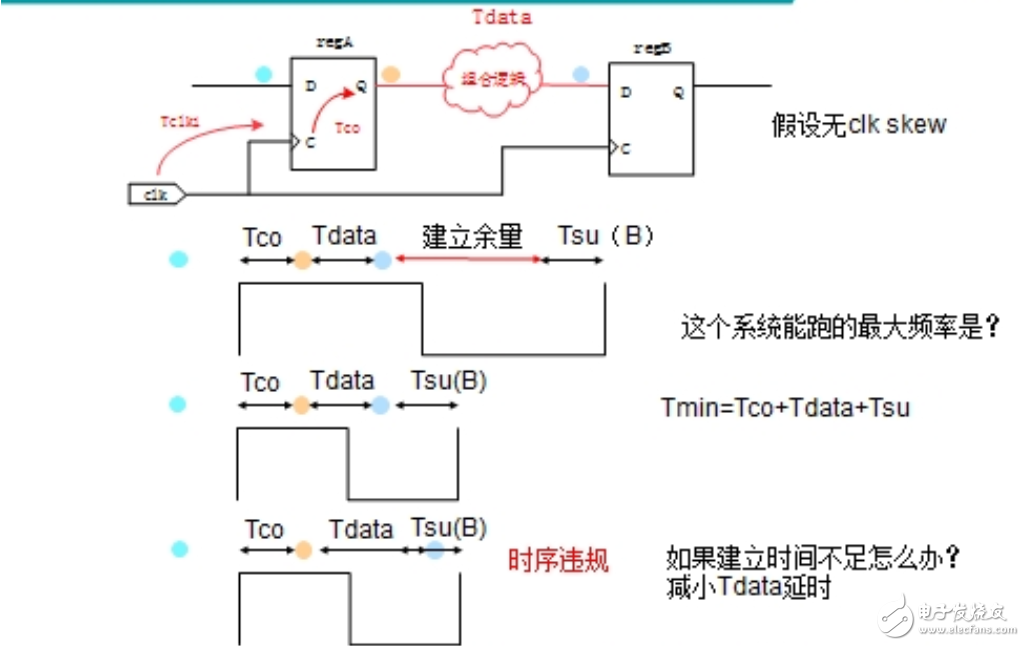

FPGA在与外部器件打交道时,端口如果为输入则与input delay约束相关,如果最为输出则output delay,这两种约束的值究竟是什么涵义,在下文中我也会重点刨析,但是前提是需要理解图1和图2建立余量和保持余量。

2019-11-10 10:06

因高速问题产生的信号过冲、下冲、反射、振铃、串扰等将严重影响系统的正常时序,系统时序余量的减少迫使人们关注影响数字波形时序和质量的各种现象。由于速度的提高使

2019-06-03 15:18

Cadence高速PCB的时序分析:列位看观,在上一次的连载中,我们介绍了什么是时序电路,时序分析的两种分类(同步和异步),并讲述了一些关于SDRAM 的基本概念。这一

2009-07-01 17:23

Cadence 高速 PCB 的时序分析 1.引言 时序分析,也许是 SI 分析中难度最大的一部分。我怀着满腔的期许给 Cadence 的资深工程师发了一封 e-mail,希望能够得到一份

2010-04-05 06:37

对于广大PCB设计工程师而言,提到时序问题就感觉比较茫然。看到时序图,更是一头雾水,感觉时序问题特别深奥。其实在平常的设计中最常见的是各种等长关系,网上流传的Layou

2012-10-22 11:51

电子发烧友网站提供《了解TI基于PCB布线规则的DDR时序规范.pdf》资料免费下载

2024-10-15 11:47

加工余量是指加工过程中从加工表面切去的金属层厚度。加工余量可分为工序加工余量和总加工余量。工序加工余量是指某一表面在一道

2022-07-10 17:05

摘要:汽车线束生产中因插接器余量设定不良造成线束分支长度不足或导线冗余是困扰很多线束企业生产的一大问题。如何合理的设置插接器余量,保证线束长度在合理的范围内是很多线束行业从业者一直致力于研究的方向

2023-07-05 10:19

本帖最后由 nanjingjing 于 2012-9-26 11:29 编辑 没布过高速板,对其pcb走线,不懂;只知道走线时,要根据文档的时序图去看一些时序参数;不知怎么看;如下的一个

2012-09-26 11:24

所示,在报告中,数据的建立时间有9~13ns的余量,而保持时间也都有7~11ns的余量,可谓余量充足。(特权同学,版权所有)图8.57 setup时序报告图8.58 h

2015-08-19 21:58