们就需要弄清楚近端串扰与远端串扰了。攻击信号的幅值影响着串扰的大小;减小串扰的途径就是

2018-10-27 09:25

在高速链路设计或者射频链路设计中,串扰是一个非常重要的分析参数。如何测量、如何分析。一般遵循着一些设计经验或者规则可以减小串扰的影响,但是很多时候却难以按照规则设计,这就会带来串

2022-08-24 09:32

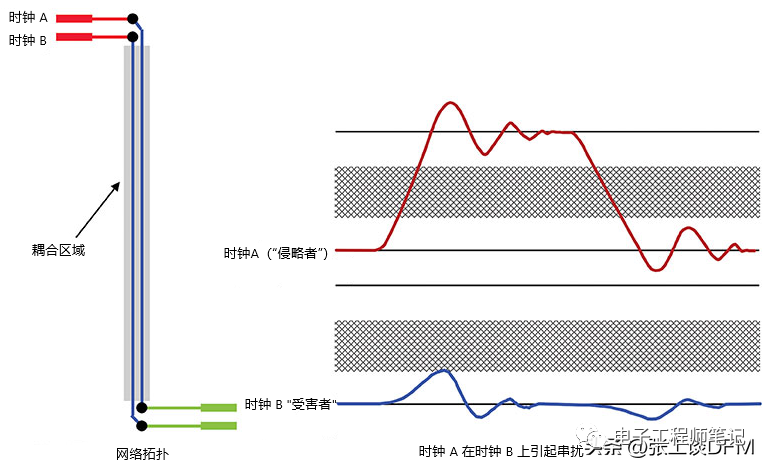

串扰是 PCB 的走线之间产生的不需要的噪声(电磁耦合)。

2023-07-20 09:57

PCB设计的首要任务是要适当地选取电路板的大小,尺寸过大会因元器件之间的连线过长,导致线路的阻抗值增大,抗干扰能力下降;而尺寸过小会导致元器件布置密集,不利于散热,而且连线过细过密,容易引起串扰。所以应根据系统所需元件情况,选择合适尺寸的电路板。

2018-03-20 15:03

耦合电感电容产生的前向串扰和反向串扰同时存在,并且大小几乎相等,这样,在受害网络上的前向串扰信号由于极性相反,相互抵消,反向串扰极性相同,叠加增强。串扰分析的模式通常包括默认模式,三态模式和最坏情况模式分析。

2019-09-19 14:39

串扰是两条信号线之间的耦合、信号线之间的互感和互容引起线上的噪声。容性耦合引发耦合电流,而感性耦合引发耦合电压。PCB板层的参数、信号线间距、驱动端和接收端的电气特性及线端接方式对串扰都有一定的影响。

2022-08-15 09:32

变化的信号(例如阶跃信号)沿传输线由A到B传播,传输线C-D上会产生耦合信号,变化的信号一旦结束也就是信号恢复到稳定的直流电平时,耦合信号也就不存在了,因此串扰仅发生在信号跳变的过程当中,并且信号沿

2018-01-26 11:03

文章——串扰溯源。 提到串扰,防不胜防,令人烦恼。不考虑串扰,仿真波形似乎一切正常,考虑了串扰,信号质量可能就让人不忍直视了,于是就出现了开头那惊悚的一幕。下面就来说说

2021-03-29 10:26

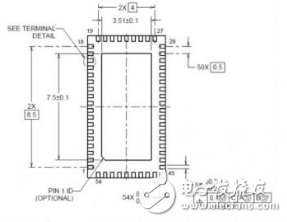

对于高速PCB中的过孔设计大部分都是通过对过孔寄生特性的分析,我们可以看到,通常在高速PCB设计的过程中,往往看似简单的过孔通常也会给电路的设计带来很大的负面效应。 所以我们为了减小过孔的寄生效应带来的不利影响

2018-01-27 10:45

串扰(Crosstalk)是指信号线之间由于互容(信号线之间的空气介质相当于容性负载),互感(高频信号的电磁场相互耦合)而产生的干扰,由于这种耦合的存在,当一些信号电平发生变化的时候,在附近的信号线上就会感应出电压(噪声),在电路设计中,抑制串扰最简单的方法就是在

2019-06-22 09:32