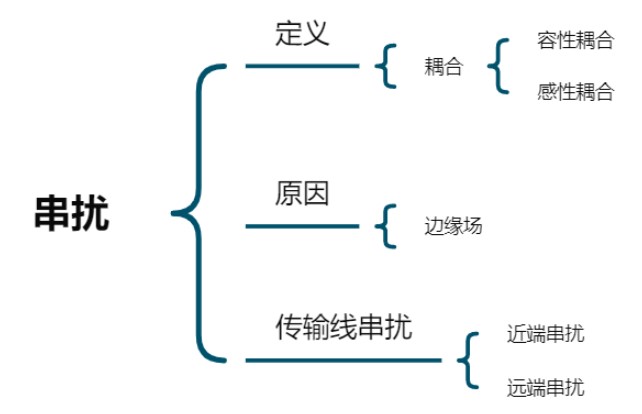

一个网络传递信号,有些电压和电流通过网络之间的耦合(容性耦合和感性耦合),传递到相邻网络,这就是串扰。

2022-08-16 09:23

阻抗匹配是指负载阻抗与激励源内部阻抗互相适配,得到zui大功率输出的一种工作状态。

2019-09-15 17:20

关于两个公式,我们不需要去记住,我们只需要知道它告诉了我们什么:攻击信号的幅值影响着串扰的大小;减小串扰的途径就是减小信号之间的耦合,增加信号与其回流平面之间的耦合。

2023-01-24 16:28

静态存储器SRAM是一款不需要刷新电路即能保存它内部存储数据的存储器。在SRAM 存储阵列的设计中,经常会出现串扰问题发生。那么要如何减小如何减小SRAM读写操作时的串扰

2020-05-20 15:24

简单地讲串扰都是因为两传输线相邻太近造成的,那么在高频走线里如何减小串扰,首先要弄清楚传输线的概念,搞清楚传输线串扰跟什么有关系。以下一些供参考。

2011-11-21 13:50

电路布线常会有串扰的风险,最后简单说明几个减小串扰的方法,常见增大走线间距、使两导体的有串扰风险的区域最小化、相邻层走线时传输线互相彼此垂直、降低板材介电常数(确保阻抗

2024-03-07 09:30

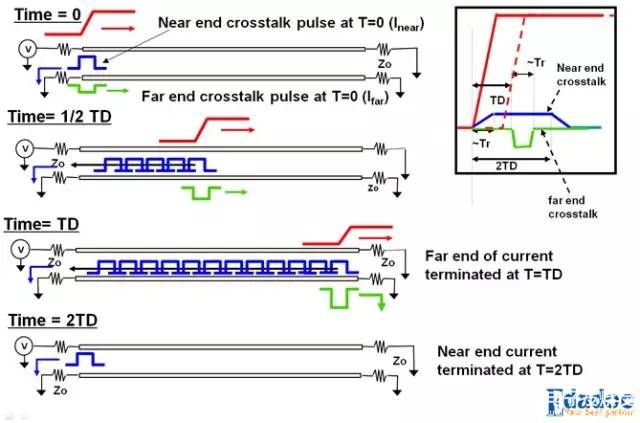

们就需要弄清楚近端串扰与远端串扰了。攻击信号的幅值影响着串扰的大小;减小串扰的途径就是

2018-10-27 09:25

做到负载匹配,通过减小反射的方法来减小串扰6.如果需要,可以进行自屏蔽7.关键信号线布在中间层(上下都是地平面);切中间层线与线的间隔要大于表层8.差分线一定要平行等长。9.走线要充分考虑回流路径,不要‘跨越’地平面

2015-03-06 10:19

在高速链路设计或者射频链路设计中,串扰是一个非常重要的分析参数。如何测量、如何分析。一般遵循着一些设计经验或者规则可以减小串扰的影响,但是很多时候却难以按照规则设计,这就会带来串

2022-08-24 09:32

高速PCB设计中,信号之间由于电磁场的相互耦合而产生的不期望的噪声电压信号称为信号串扰。串扰超出一定的值将可能引发电路误动作从而导致系统无法正常工作,解决PCB串

2020-07-19 09:52