在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果

2019-03-15 14:05

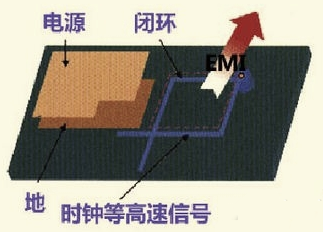

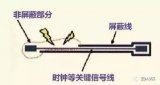

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没有屏蔽或只屏蔽了部分,都是会造成EMI的泄漏。

2019-12-16 14:52

布线(Layout)是PCB设计工程师最基本的工作技能之一。走线的好坏将直接影响到整个系统的性能,大多数高速的设计理论也要最终经过Layout得以实现并验证,由此可见,布线在高

2019-07-01 15:24

解决。 高速信号走线屏蔽规则 如上图所示:在高速的PCB设计中,时钟等关键的高速

2023-05-22 09:15

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果

2019-05-06 18:08

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽处理,如果

2017-08-25 15:35

在 PCB 设计中,等长走线主要是针对一些高速的并行总线来讲的。由于这类并行总线往往有多根数据信号基于同一个时钟采样,每个时钟

2020-11-22 11:54

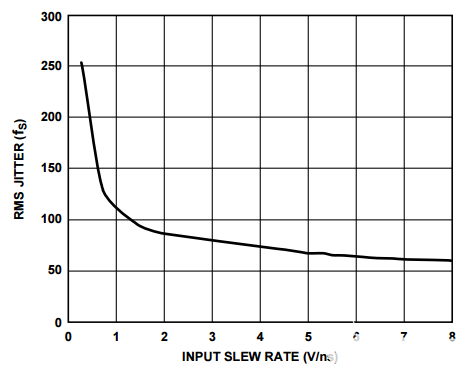

PCB走线的行为类似于低通滤波器,当时钟信号沿走线行进时会衰减,并随着走线长度的增加而增加脉冲边沿失真。较高频率的时钟信

2023-01-30 11:48

高速讯号会导致PCB板上的长互连走线产生传输线效应,它使得PCB设计者必须考虑传输

2018-05-22 07:18

所有的高速信号必须有良好的回流路径,尽可能地保证时钟等高速信号的回流路径最小,否则会极大的增加辐射,并且辐射的大小和信号路径和回流路径所包围的面积成正比。

2019-04-03 09:30