高速时钟线的处理.pdf

2014-01-08 15:04

规则一:高速信号走线屏蔽规则 在高速的PCB设计中,时钟等关键的高速信

2017-11-25 07:43

在高速的PCB设计中,时钟等关键的高速信号线,走线需要进行屏蔽

2019-03-15 14:05

在高速的 PCB 设计中,时钟等关键的高速信号线,走线需要进行屏蔽

2024-01-10 16:03

在高速的PCB设计中,时钟等关键的高速信号线,走需要进行屏蔽处理,如果没

2019-12-16 14:52

线,通常它不需经过任何其它逻辑处理,因而其延时会小于其它相关信号。高速数字PCB板的等线长是为了使各信号的延迟差保持在一个范围内,保证系统在同一周期内读取的数据的有效性

2019-05-21 07:14

各位,请教问题哈:我们通常说的高速时钟线,多少M的算高速,多少M的算低速?比如说我一个板子跑的最高速是100Mhz,我的

2020-08-17 08:04

由于 PCB 板的密度越来越高,许多 PCB LAYOUT 工程师在走线的过程中,较容易出现一种失误,即时钟信号等高速信

2024-01-08 15:33

滤波电容,如VTT等。这不仅对稳定性有影响,对EMI也有很大的影响。 2 时钟线的处理 2.1)建议先走时钟线。

2018-09-11 16:05

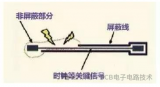

规则一:高速信号走线屏蔽规则 如上图所示: 在高速的PCB设计中,时钟等关键的高

2020-02-14 11:53