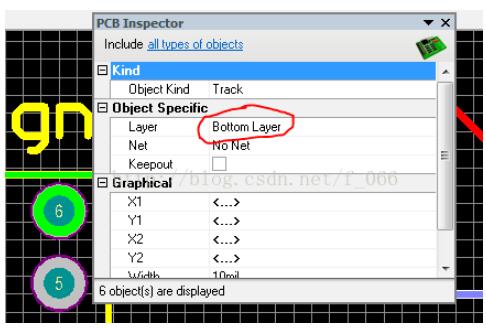

本文主要详细介绍了pcb顶层和底层互换,把PCB切换到顶层,然后Edit/select/allonlayer选择顶层。

2019-04-26 15:47

我们将对多层电路板进行射频线仿真,为了更好的做出对比,将仿真的PCB分为表层铺地前的和铺地后的两块板分别进行仿真对比;表层未铺地的

2018-04-09 15:54

首先将线宽不同的两块板(表层铺地前)由ALLEGRO导入SIWAVE,在目标线上加入50Ω端口。针对不同线宽0.1016mm和0.35mm, 我们的仿真结果如图2所示,图中显示的曲线是S21,仿真频率范围为800MHz-1GHz。

2019-09-17 14:42

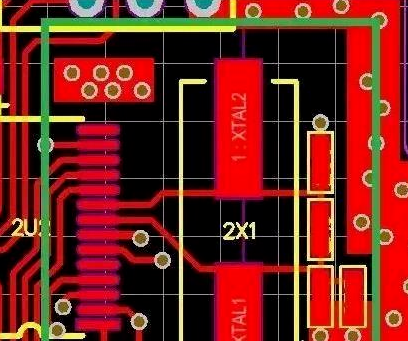

时钟晶体下面铺地和走线

2023-11-24 15:37

EDA(电子设计自动化)顶层丝印层是在PCB(Printed Circuit Board,印刷电路板)设计过程中起到标记和辅助引导功能的一层。它通常包含了元件名称、位置、方向和标志等信息,对于电路板

2023-12-19 17:30

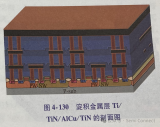

顶层金属工艺是指形成最后一层金属互连线,顶层金属互连线的目的是实现把第二层金属连接起来。顶层金属需要作为电源走线,连接很长的距离,需要比较低的电阻,需要很大的宽度以支持很大的电流。

2024-10-29 14:09

顶层金属 AI工艺是指形成顶层金属 AI 互连线。因为 Cu很容易在空气中氧化,形成疏松的氧化铜,而且不会形成保护层防止铜进一步氧化,另外,Cu 是软金属,不能作绑定的金属,所以必须利用AL 金属

2024-11-25 15:50

能够创建、管理和文档不同的设计变量重要的是要确保他们生产没有缺陷。看看可以简化为任何PCB定义多个变量的过程。

2019-10-23 07:02

众所周知,企业数字化转型是一个复杂的系统工程,其中顶层设计更是起着把方向、定目标、绘蓝图、指路径的重要作用。但顶层设计不是闭门造车,需要在实践中不断探索;也并非一日而成,需要在探索中持续优化。

2021-03-01 10:36

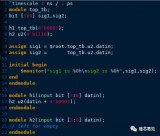

示例中,在顶层top_tb中例化了两个module(h1和h2),例化名分别是top_tb和u2,其中h1中又例化了h2,也就是h2在顶层top_tb和h1中分别进行了例化,在例化时分别传递了对应的参数。其中h1和h2在各层次的例化属于“显式例化”,整个代码的层次

2023-04-28 10:28